# Next Generation IC Technology Challenges and Opportunities

### 刘晓芹

大中华区总经理,Ansys电子与半导体事业部 清华大学下一代芯片技术3DIC/Chiplet学术研讨会 2022/10/28

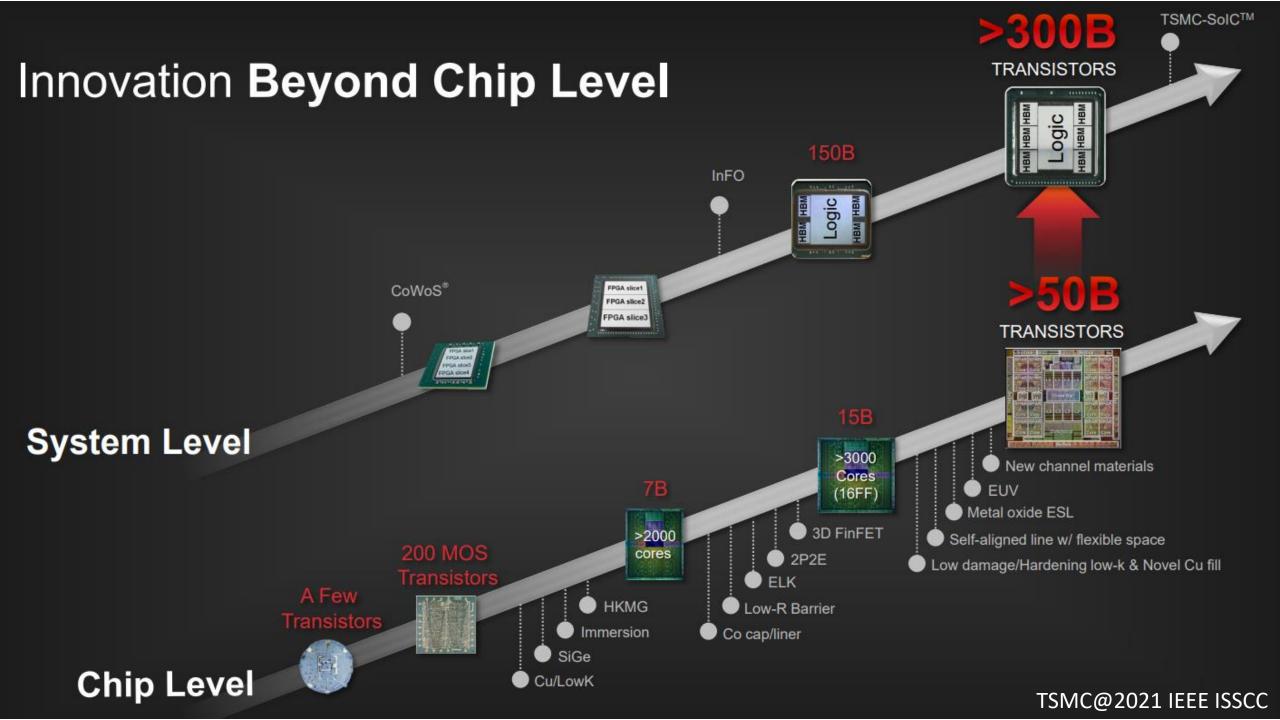

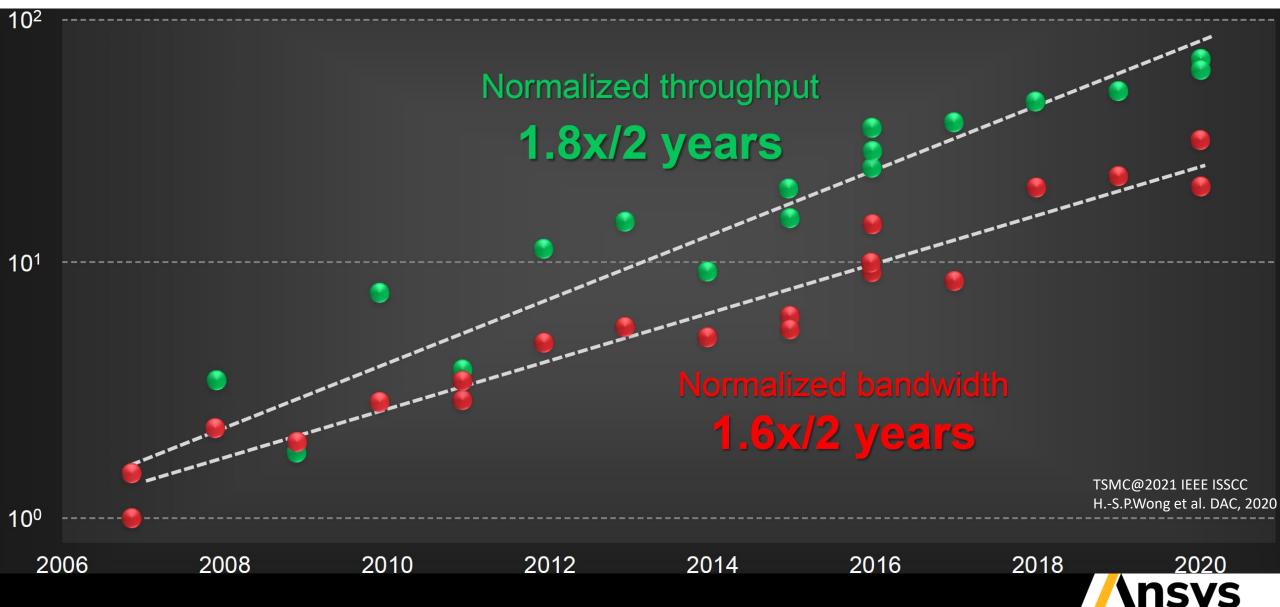

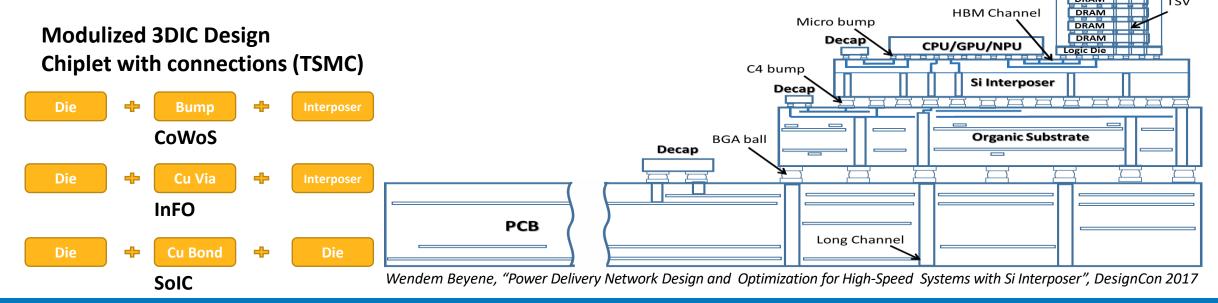

### Bandwidth Deficit Limits System Throughput – MORE I/O DENSITY

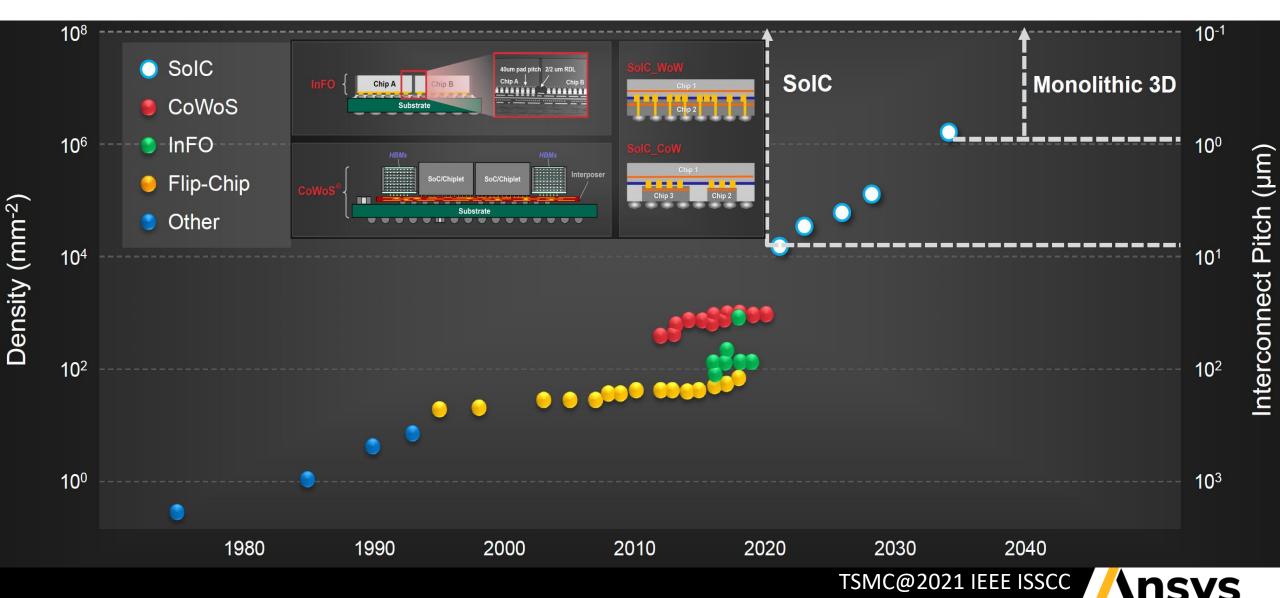

### Advanced Packaging for Another 10,000X I/O Density Increase

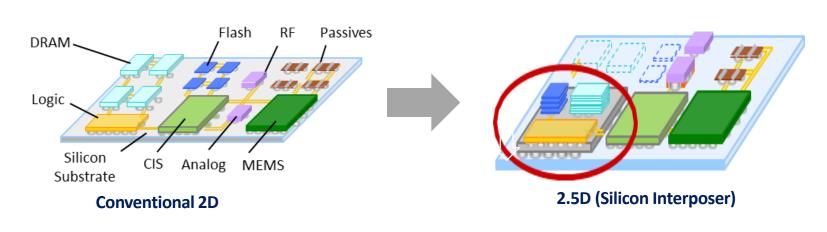

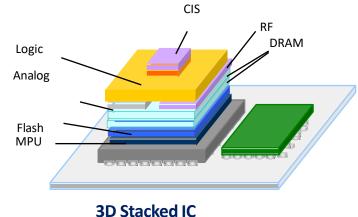

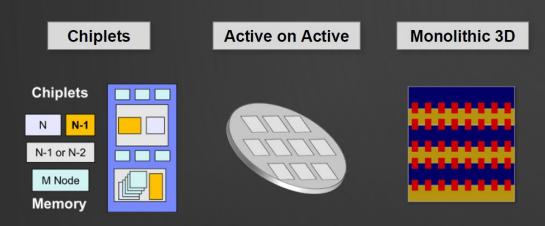

## Pros and Cons of 3DIC/2.5DIC with Chiplet

### **Building Chip like Modulized Software Programming!**

Courtesy of TSMC Reference Flow

| Pros                                                             | Cons                                                                       |

|------------------------------------------------------------------|----------------------------------------------------------------------------|

| Small form factor                                                | <ul> <li>Small heat sink area =&gt; Heat accumulation (Thermal)</li> </ul> |

| <ul> <li>Short channel length &amp; propagation delay</li> </ul> | <ul> <li>Design implementation is hard</li> </ul>                          |

| <ul> <li>Lower power, higher bandwidth</li> </ul>                | High complexity                                                            |

| High system performance                                          | <ul> <li>Difficult to analyze, verify and signoff (and testing)</li> </ul> |

| • With Chiplet: Reusable, higher yield,                          | With Chiplet: More testing, Connection                                     |

| higher IO density/bandwidth                                      | design/verification/manufacturing, thermal                                 |

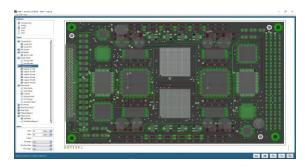

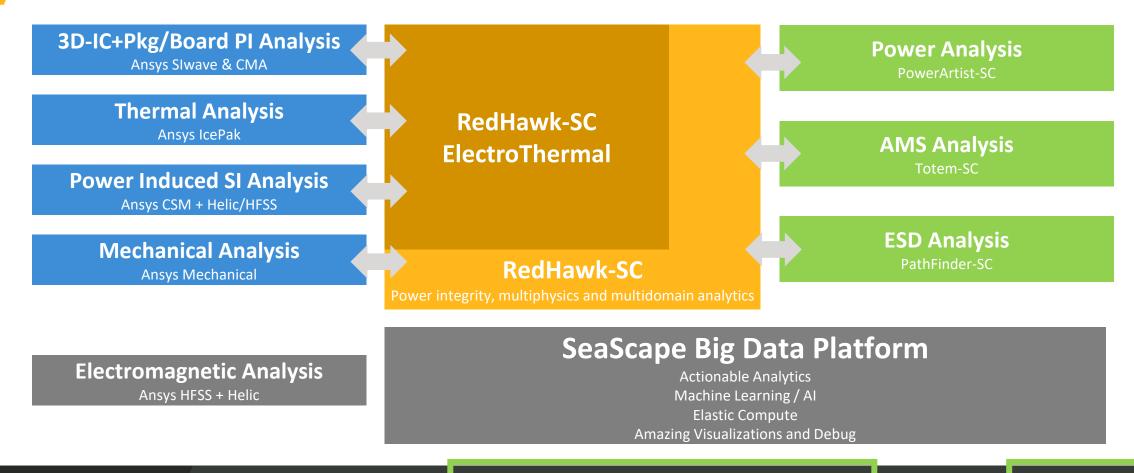

### Eco System for 2.5D/3D IC Power, Signal and Thermal Integrity

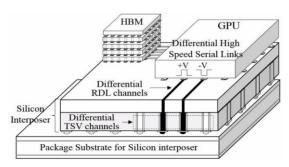

- 1. Modeling connectivity of complicated 3DIC structure

- 2. Parasitic modeling of packages (Interposer, FOWLP), board PCB

- 3. Power, signal and thermal modeling of interconnects of stacked dies

- 4. Noise source modeling for power, signal and thermal

- 5. Interface connection (Bump, Ball and TSV) modeling

Need for accurate and easy set up for chip, package and board co-simulation Comprehensive chip, package and system co-design and co-analysis is necessary

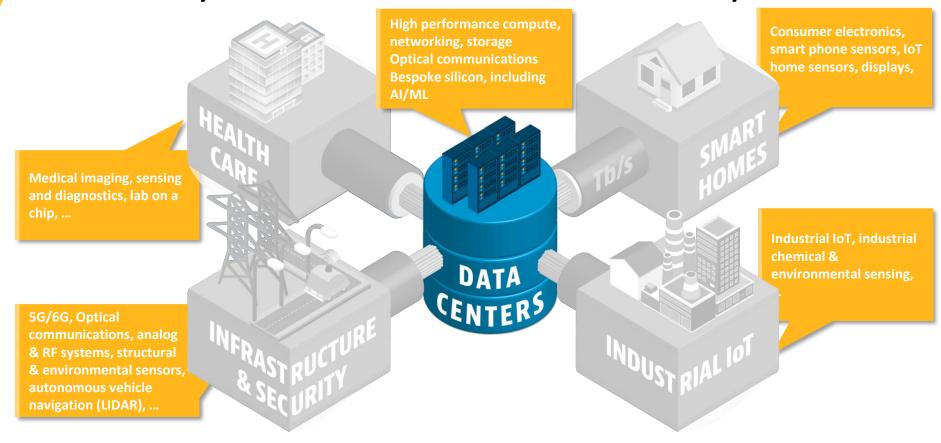

### Data – Key Driver For Information Society

Data Sensing, Reception, Transmission and Processing (Electromagnetics, Optics, Electronics, Semiconductors)

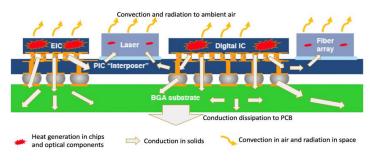

### Integration Beyond Electronics and Semiconductors – w/ Optics

**RF, PMIC, AMS**

FinFET and 3D-IC

**Chip-Package-Board**

**Co-packaged electro-optical**

5G/6G and Edge IoT

**HPC and Cloud**

Automotive, Aerospace and Industrial

Multiphysics Solutions for SI/PI/TI/Reliability (Electromagnetics, Optics, Thermal) x (Die, 3D-IC, Package, Board)

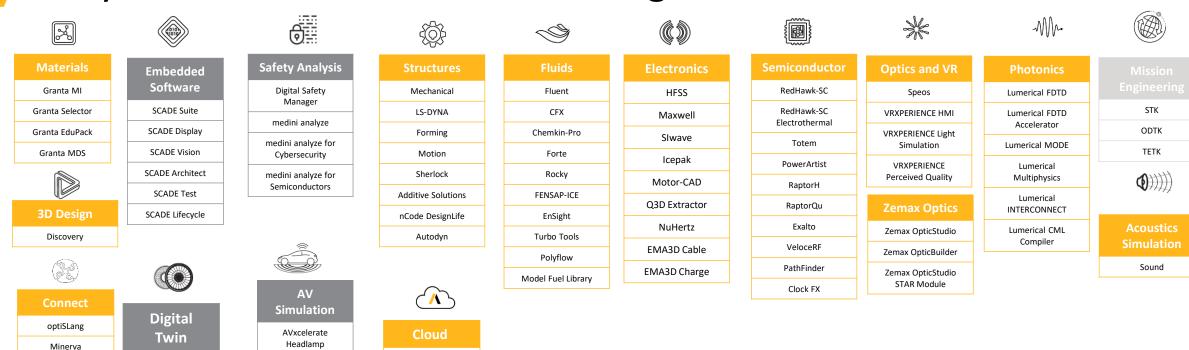

### Ansys – A Hub For Scientists and Engineers

**Ansys Cloud**

### Ansys - one of the Big-4 EDA companies

Twin Builder

Revenue: ~\$2B EDA, major 3DIC/Chiplet Multiphysics solution provider

**AVxcelerate Sensor**

One of Four Major EDA companies for Leading Foundry Golden Solution Certification

ModelCenter

### Ansys SeaScape Platform for Chiplet/3DIC-Centric Multiphysics

PHYSICS-BASED SIMULATION

**STRUCTURES**

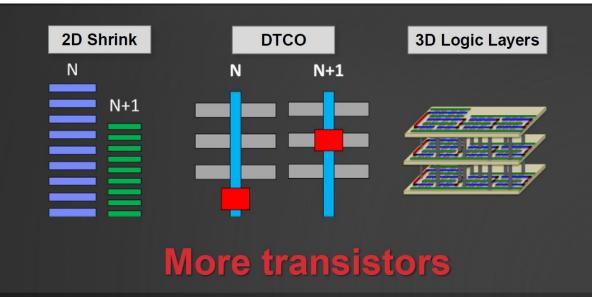

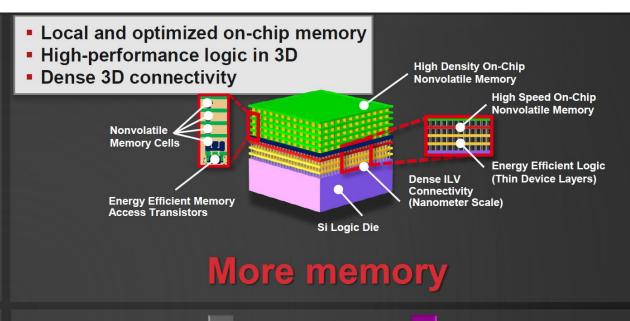

### The Future is SYSTEM INTEGRATION

**Logic-memory integration**

**End-to-end optimization**

TSMC@2021 IEEE ISSCC /\nsys

# **Ansys**