# Victim Alignment in Crosstalk-Aware Timing Analysis

Ravikishore Gandikota, Kaviraj Chopra, David Blaauw, Senior Member, IEEE, and Dennis Sylvester, Senior Member, IEEE

Abstract-Modeling the effect of coupling-noise on circuit delay is a key issue in static timing analysis and involves the victim-aggressor alignment problem. As delay-noise strongly depends on the skew between the victim-aggressor driver input transitions, it is not possible a priori identify the victim-driver input transition that results in the worst-case delay-noise. Several approaches have been proposed in literature which heuristically search for the worst-case victim-aggressor alignment. This paper presents an analytical result that obviates the need to search for the optimal victim-driver input transition, thereby simplifying the victim-aggressor alignment problem significantly. Using the properties of standard nonlinear complementary metal-oxide semiconductor drivers, it is shown that for monotonic input transitions the worst-case victim-driver input transition is the one that switches at the latest point in its timing window. Similarly, the victim-driver input alignment at the earliest point in the timing window is optimal for early-mode analysis. Although this result has been empirically observed in the industry, to the best of our knowledge this is the first paper which provides a rigorous analysis and shows that the above result holds for both linear and nonlinear drivers. It is also shown that the latest alignment of the victim-driver input transition results in the latest victim receiver output arrival time even for the cases where the victim is coupled to *multiple* aggressors. Finally, experimental results show that limiting the alignment of the victim to only the latest victim-driver input transition can significantly reduce the runtime of existing approaches with no loss of accuracy.

*Index Terms*—Computer-aided design, crosstalk, timing, very large-scale integration.

#### I. INTRODUCTION

CALING of device dimensions into the nanometer regime has led to a considerable reduction in the gate delays. However, interconnect delay has not scaled in proportion to gate delay and global interconnect delay now accounts for the major portion of the total circuit delay. Due to process-technology scaling, the spacing between adjacent interconnect

Manuscript received March 11, 2008; revised July 4, 2009. Current version published January 22, 2010. This paper extends the work published in the 2007 International Conference on Computer Aided Design (pp. 698–704). This paper was recommended by Associate Editor C. V. Kashyap.

R. Gandikota, D. Blaauw, and D. Sylvester are with the Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI 48105 USA (e-mail: gravkis@umich.edu; blaauw@umich.edu; dennis@eecs.umich.edu).

K. Chopra is with Mentor Graphics, San Jose, CA 95131-2314 USA (e-mail: kaviraj.chopra@gmail.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCAD.2009.2035484

wires keeps shrinking which leads to an increase in the amount of parasitic coupling capacitance between the wires. In [1] it was reported that, in 90 nm technology node, coupling capacitance accounts for more than 85% of the total interconnect capacitance. A more aggressive technology scaling will only lead to an increase in the overall contribution of the coupling capacitances. Therefore, capacitive-coupling-noise has become an important issue when performing timing verification of physical designs. Due to capacitive-coupling, the switching characteristic of a net is affected by the simultaneous switching of nets which are in close physical proximity. The net under analysis is referred to as the victim and all neighboring nets are termed as aggressors. The coupling-noise injected by an aggressor can either slowdown or speedup the victim transition depending on the mutual victim-aggressor switching directions. The change in the victim arrival time (usually the time at which it crosses 50% of supply voltage) is referred to as delay-noise. It is important to quantify the maximum delay-noise while performing static timing analysis (STA) for design sign-off.

Static coupling-noise analysis was first introduced in [2], [3] and since then it has been the focus of significant research efforts. As delay-noise requires the aggressor and victim nets to switch in close temporal proximity of each other, the concept of timing windows was developed to identify the interval of the clock period within which a net can transition. Consequently, we can ignore those aggressors whose timing windows do not overlap with the victim timing window. However, it was observed that the computation of delay-noise and timing windows is not mutually independent. Delay-noise cannot be computed before the timing windows are defined, and conversely timing windows cannot be computed without any information about the delay-noise. However, in [4]-[6] it was shown that this *chicken-and-egg* problem can be solved using an iterative approach. The iterations start with either the assumption that all aggressor timing windows overlap with that of the victim, or that there is no overlap between the victimaggressor timing windows. In each iteration, the worst-case victim-aggressor alignment is determined by updating the timing windows with delay-noise computed in the previous iteration. Delay-noise is then recomputed and then timing windows are updated accordingly until the two converge. It was shown in [4] that this iterative method is guaranteed to converge and in [6] it was theoretically established that timing analysis with crosstalk is a fixpoint solution on a complete lattice.

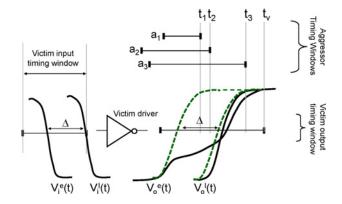

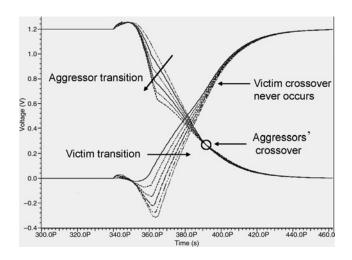

A fast and accurate delay-noise computation engine is key since the delay-noise engine is present in the inner loop of noise analysis. We know that delay-noise is very sensitive to the skew between the aggressor and victim arrival times. Therefore, it is not trivial to find the worst-case alignment between the aggressor and the victim transitions, such that the output arrival time of the noisy victim is maximized [7], [8]. For a better understanding of the problem, consider two transitions at the input of the victim-driver, one switching earlier than the other (as shown in Fig. 2). If the early victim transition couples more strongly with an aggressor or aligns with additional aggressors, then its delay-noise can be larger when compared to that of the later victim transition. However, it is not clear if a greater coupling-noise in the earlier transition can result in a later victim arrival time. Hence, it is difficult a priori determine which victim-driver input arrival time will produce the latest victim arrival time. Therefore, in order to determine the worst-case alignment of the victim transition, we must compute the maximum delay-noise for both the victim transitions and then pick the one which results in the latest output arrival time.

Initial approaches for performing delay-noise analysis ([4], [9]–[11]) used coupling factors (e.g., 0–2) to appropriately scale the coupling capacitance. However, delay-noise depends on numerous factors such as the victim–aggressor alignment, the slew rate, and the drive strength of the victim–aggressor pair. Therefore, delay-noise analysis performed by simply scaling the coupling capacitances does not provide adequate accuracy. In [12], [13], a relative window-based approach is proposed where the delay-noise is obtained as a function of the relative window for every aggressor–victim pair. The dependence of delay-noise on the alignment can be computed by using simulation program with integrated circuit emphasis (SPICE)-based simulations [14] or derived analytically using curve-fitting techniques [15].

A brute-force solution to the victim-aggressor alignment problem can be obtained by sweeping the victim arrival time exhaustively within its timing window, finding the worst-case aggressor alignment for each victim transition and selecting the one which results in the latest victim arrival time. Since an exhaustive sweep is not practical for large circuits, several heuristic methods have been proposed in [7], [16]–[18]. The authors formulate the alignment problem as a weighted channel density problem in [16] and an empirical model-based approach is used to predict the alignment in [7]. An effective skew window model was proposed in [17] which however leads to a pessimistic estimation of delay-noise. In [18] the concept of effective delay-noise was introduced to eliminate the pessimism by capturing the maximum change in the victim timing window due to coupling-noise. Recently, in [19] the authors solve the alignment problem as a constrained optimization problem by using nonlinear simulations for evaluating the nonlinear objective function.

All the approaches outlined above either present a heuristic or perform a computationally expensive search in the victim timing window to solve the victim–aggressor alignment problem. In contrast to these, we present in this paper an analytical result that obviates the need to enumerate the victim transitions

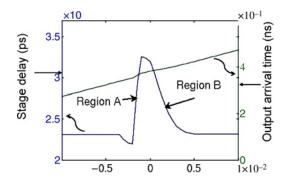

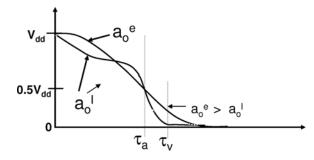

Fig. 1. Stage-delay and output arrival time of a victim as a function of the skew between victim-aggressor driver input transitions.

within in its timing window. Using the properties of standard nonlinear complementary metal-oxide semiconductor (CMOS) drivers, we show that for late-mode analysis the latest output arrival time of a victim net occurs only when the victimdriver input transition occurs at the latest point in its timing window. Similarly, it can be proved that the victim alignment at the earliest point in the timing window is optimal for earlymode analysis. Since we only need to compute the worstcase alignment of the aggressors, the alignment problem is now significantly simplified. This result has been empirically observed in the industry1 and is already used in certain industrial noise analysis tools as an efficient heuristic to avoid enumerating the victim timing window. However, to the best of our knowledge this is the first paper which analytically shows that the above result is optimal for both linear and nonlinear driver models. While the proof is fairly straight forward for linear driver models, it is not trivial for nonlinear drivers which are the cases of practical concern.

Delay-noise is a function of the victim-aggressor alignment and the delay-noise could decrease (due to misalignment) if the victim-driver input arrival time is increased. However, we analytically show that this decrease in delay-noise is always less than the shift in the victim-driver input arrival time. Using this result we show that in order to maximize the victim arrival time, we must always align the victim-driver input transition at its latest possible arrival time. This significantly reduces the complexity of the victim-aggressor alignment problem, since we no longer need to search for the optimal victim transition within its timing window. Furthermore, the total number of aggressors which couple noise to the latest occurring victim transition is always less than the number that are coupled to a victim transition that can occur at any point in its timing window. Using the above approach, we show results that lead to significant speedups in delay-noise analysis over existing approaches without compromising any accuracy.

### II. PROBLEM DESCRIPTION

The focus of this paper is to find the optimal alignment of the victim transition for delay-noise analysis. In this paper,

<sup>1</sup>The fact that the latest alignment result was empirically known in the industry was conveyed to us through personal communication and reviewer feedback.

we analyze the case when the victim and the aggressor are switching in mutually opposite directions. In particular, we want to solve for a victim-driver *input* arrival time such that the delay-noise results in the *latest* victim arrival time. A similar analysis can be performed to find the earliest victim arrival time with both the victim and the aggressor nets switching in the same direction.

In Fig. 1, we can see the plot of the victim stage delay as a function of the difference between the input arrival time of the victim and the aggressor drivers (referred to as the input skew). For large values of both positive and negative input skew, there is no temporal overlap between the victim–aggressor transitions. Therefore, the victim stage delay remains unchanged and is given by the nominal delay. However, for smaller values of input skew when both the victim and the aggressor switch in close temporal proximity, the aggressor transition couples noise to the victim transition and subsequently changes its stage delay. The small dip in the stage delay plot at zero skew is due to the Miller feed-through effect which causes (for instance) the falling aggressor signal to initially overshoot above the supply voltage and consequently speeds up the victim transition.

As a thought experiment, suppose that we have a fixed aggressor-driver input transition and that we can change the arrival time of the victim-driver input transition. In Region A of the plot, the victim stage delay increases with an increase in its input arrival time. This happens because the temporal overlap between the victim-aggressor transitions increase as the victim transition is further delayed in time. Once the victim and the aggressor transitions are optimally aligned and the victim stage delay peaks, any further increase in the victim-driver input arrival time leads to misalignment. Consequently, this leads to a decrease in the stage delay (in Region B) due to a reduction in the amount of delay-noise.

Now, suppose that the magnitude of the slope in Region B is always less than one. In other words, the decrease in the stage delay in Region B is always less than the increase in its input arrival time. Since the output arrival time is the sum of the input arrival time and the stage delay, the victim arrival time will always be a monotonic increasing function of the victim-driver input arrival time. Therefore, the latest victim arrival time will occur only when the victim-driver input transition occurs at the latest possible time (i.e., the latest point in its timing window). However, it is nontrivial to show that the magnitude of the slope in Region B is always less than one. It is especially difficult to show that the above holds for nonlinear drivers, since the analysis is complicated by the cyclic nonlinear dependency between the aggressor and the victim responses [19].

For example, consider the aggressors  $a_{1-3}$  coupled to a victim net and their respective timing windows (as shown in Fig. 2). The timing window of a net represents an interval of the clock period within which the net can transition. In this paper, we define the timing window of a victim as the time interval between the 50% crossing times of the earliest and latest victim transitions. A pessimistic estimate of the earliest/latest transitions (hence timing windows) for every net can be obtained by performing block-based STA on the circuit.

Fig. 2. Victim alignment for worst-case delay and possible crossover of noisy output transition.

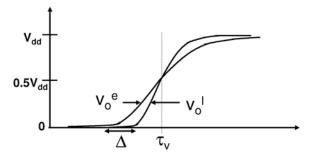

Let  $v_i^l(t)$  be the falling victim-driver input transitions which occurs at the latest point in its timing window. Now, consider another transition  $v_i^e(t)$  which switches earlier than  $v_i^l(t)$  by an amount  $\triangle$ . From causality arguments, the *noiseless* victim transitions (dashed waveforms) must also be separated by  $\triangle$ . It can be seen that the noisy output transition  $v_o^e(t)$ , corresponding to the early victim-driver input transition, intersects with the timing windows of all three aggressors  $a_{1-3}$ . However, when the victim-driver input transition is delayed, the resulting output transition  $v_o^l(t)$  can only couple with aggressor  $a_3$ . Consequently, the delay-noise observed for  $v_o^e(t)$  is greater than that of  $v_o^l(t)$ . In such a case, if the difference between the delay-noise of  $v_o^e(t)$  and  $v_o^l(t)$  is greater than  $\triangle$ , then the victim waveforms will cross each other (as shown in Fig. 2). Therefore, for cases when there are multiple aggressors coupled to the victim, it is not necessary that the output arrival time of  $v_o^l(t)$  must always be later than that of  $v_o^e(t)$ .

If we want to find the latest victim arrival time, we must allow any feasible victim transition occurring within its timing window. Furthermore, for each victim transition, we need to find the alignment of the aggressors such that delay-noise is maximized. However, sweeping the victim transition and computing the alignment of aggressors at each point is not feasible, in particular for nonlinear driver models which require timeconsuming nonlinear simulations. As a result several heuristic solutions [17], [18] have been proposed to avoid an exhaustive search in the victim timing window. In [18], the authors proposed to enumerate victim alignment at the end points of victim and the aggressor timing windows. For example, in Fig. 2 this would require the alignment of the victim transition at four different arrival times  $t_1$ ,  $t_2$ ,  $t_3$ , and  $t_v$ . For each victim alignment we find the worst-case alignment of all the aggressors and compute the worst-case delay-noise. Finally, the victim-aggressor alignment which results in the maximum victim arrival time is chosen. The complexity of the above approach is  $O(n^2)$ , where n refers to number of aggressors coupled to the victim. Since, the worst-case alignment of the aggressors has to be recomputed for every victim transition, the above approach can turn out to be very computationally expensive. Also, such heuristic techniques cannot guarantee the optimality of the results since we have not considered all feasible victim-driver input transitions in the timing window (only four in the above example).

In this paper, we show that the magnitude of slope of the curve in Region B (of Fig. 1) can never be greater than one. This means that if the victim-driver input is delayed and the delay-noise decreases due to misalignment, then this decrease is not sufficient to compensate for the fact that this victim transition now starts later. This leads to the useful result that the worst-case victim alignment can occur only when the victim-driver input is aligned at its latest arrival time. Consequently, even with nonlinear victim-aggressor drivers, any search of victim alignment within its timing window is not necessary and we can safely align the victim-driver input transition at the latest point in its timing window. This significantly speeds up the noise analysis since we only need to find the worst-case aggressor alignment for only a single victim transition. While this result has been empirically observed in industrial computer-aided design tools, to the best of our knowledge, this is the first paper which proves that the above result holds for both linear and nonlinear driver models. Our proof is based on simple properties of standard nonlinear CMOS drivers which are discussed in Section IV-A. It must be noted that the above proof may not apply when multipleinput switching effects are considered. We also discuss the assumption of monotonicity in the victim-aggressor driver input transitions in Section III.

The remainder of the paper is organized as follows: Section III proves the victim alignment result assuming linear driver models. Section IV forms the core of this paper, where we prove this result for the more general case of nonlinear CMOS drivers. It will be shown that the latest victim alignment result which maximizes the victim arrival time also implicitly maximizes the victim *receiver* output arrival time. In Section V, we extend the proof for the case when the victim is coupled to multiple aggressors. Results shown in Section VI confirm the efficacy of the proposed approach and we state our conclusions in Section VII.

#### III. VICTIM ALIGNMENT FOR LINEAR DRIVERS

It is well-known that nonlinear driver models [16], [19], [20] provide better accuracy in timing analysis than linear driver models. Nevertheless, linear driver models with time-invariant constant resistances are still being used in existing industrial tools [21] for fast analysis in the early stages of design. For linear driver models, superposition principle can be used to break the cyclic dependency between the aggressor and victim responses. This simplifies the analysis for finding the worst-case victim–aggressor alignment. In this section we prove that for linear drivers, the latest victim arrival time occurs only when the victim-driver input transition is aligned at the latest arrival time. We will later review the victim alignment for the more general case of nonlinear time-varying driver models in Section IV.

In delay-noise analysis, as is currently practiced [4]–[6], it is assumed that the aggressor/victim-driver input transitions can occur at any point within its timing window and are independent of each other. Hence, all possible permutations consisting of any possible aggressor/victim-driver input transition combination are feasible. Among these possible aggres-

sor/victim driver input transition pairs, the pair that results in the *latest* victim transition needs to be determined for worst-case noise analysis. Given all possible victim/aggressor driver input transition permutations, we show in this section that only that subset of permutations, where the victim-driver input transition is aligned at its latest arrival time, needs to be considered in worst-case noise analysis.

Theorem 1: Given linear victim-aggressor driver models and monotonic victim-driver input transitions, the victim transition obtained by aligning the victim-driver input transition at the latest point in its timing window bounds all possible victim transitions.

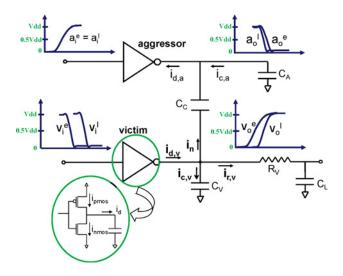

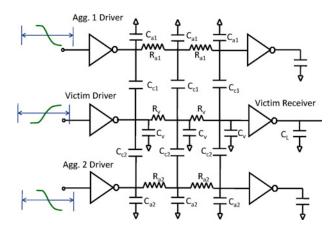

*Proof:* Consider the victim-aggressor configuration as shown in Fig. 3 where we have linear victim and aggressor drivers. Without loss of generality, we assume monotonic falling victim and a rising aggressor driver input transition with inverting aggressor-victim-drivers. Let  $v_i^l(t)$  be the latest occurring monotonic victim-driver input transition that is aligned at the latest arrival time in its timing window. Also, let  $v_i^e(t)$  be any earlier input transition occurring anywhere within its timing window. A necessary condition for the above theorem to be valid is that the latest (falling) victim-driver input transition  $v_i^l(t)$  always bounds any earlier input transition  $v_i^e(t)$ , i.e.,

$$v_i^l(t) \ge v_i^e(t) \quad \forall t. \tag{1}$$

In STA framework, only the bounds on the early/late arrival times are propagated and we have no information about the slews of other feasible transitions that can occur inside the timing window. Nevertheless, current noise analysis tools are often required to simulate the victim-driver input transition at all or many points inside the timing window. Hence, the typical assumption in noise analysis in this situation is to use the slew of the victim-driver input transition  $v_i^l(t)$ . In effect, this means that any earlier victim-driver input transition  $v_i^e(t)$  is a time shifted version of the latest victim-driver input transition  $v_i^l(t)$ , and (1) holds true for nonmonotonic input waveforms.

Let the corresponding early/late victim transitions be denoted by  $v_o^l(t)$  and  $v_o^e(t)$ , respectively. Our goal is to show that the latest rising victim transition  $v_o^l(t)$  bounds any earlier victim transition  $v_o^e(t)$ , expressed mathematically

$$v_o^l(t) \le v_o^e(t) \quad \forall t.$$

(2)

We prove the above claim by taking any arbitrary aggressor-driver *input* transition occurring anywhere within its timing window. Then, for this particular aggressor-driver input transition, we show that the worst-case victim-driver input transition is the one aligned at the latest point in its timing window. Now, since the above result holds for all feasible aggressor-driver input transitions, it follows that only the victim/aggressor driver input transition pairs with the victim-driver input transition aligned at it latest arrival time needs to be considered in worst-case noise analysis.

As mentioned above, it is necessary to show that (2) holds for all feasible aggressor transitions. Therefore, we do not impose any restrictions on the aggressor input transition and allow it to occur anywhere within its timing window. Applying

Fig. 3. Coupled victim-aggressor configuration.

the principle of superposition which holds for linear driver models, the noisy victim transition  $v_a^l(t)$  can be written as

$$v_o^l(t) = \bar{v}_o^l(t) + v_n(t) \tag{3}$$

where  $\bar{v}_o^l(t)$  is the noiseless victim transition obtained with a quiet aggressor and  $v_n(t)$  is the noise waveform coupled to a quiet victim. Since the aggressor input is the same and the victim-driver resistance is modeled as a linear constant, the noise  $v_n(t)$  is the same in both (early/late) cases. Therefore, the early victim noisy output transition  $v_o^e(t)$  is given by

$$v_o^e(t) = \bar{v}_o^e(t) + v_n(t).$$

(4)

Since the inputs are falling monotonically, the noiseless output transitions must therefore be rising monotonically. From causality, it follows from (1) that the late noiseless output transition always bounds the early noiseless output transition

$$\bar{v}_o^e(t) \geq \bar{v}_o^l(t) \quad \forall t.$$

(5)

As the noise  $v_n(t)$  remains the same since we assume linear drivers, inserting (3) and (4) into the above equation, it follows that the noisy output transition  $v_o^l(t)$  bounds  $v_o^e(t)$

$$v_o^e(t) \ge v_o^l(t) \quad \forall t.$$

(6)

Since the late victim transition  $v_o^l(t)$  is always less than the early victim transition  $v_o^e(t)$ , it will always cross the 50% (or any other) supply voltage point later than  $v_o^e(t)$ . Therefore, the latest victim arrival time can occur only when the victim-driver input transition is aligned at the latest possible input arrival time.

#### IV. VICTIM ALIGNMENT FOR NONLINEAR DRIVERS

In order to model the nonlinearity of CMOS drivers in noise analysis, nonlinear driver models such as current source models [19], [20], [16] have recently been developed which provide much better accuracy than linear models. In this section, we show that the victim alignment result derived in the previous section also holds for nonlinear drivers. We begin

this section by describing the characteristics of CMOS driver output current.

## A. Properties of Nonlinear Drivers

In order to derive the latest victim alignment result, we consider a nonlinear inverting CMOS driver where  $i_d(t) = f(v_i(t), v_o(t))$  is the *steady-state* current flowing out of the driver,  $v_i(t)$  and  $v_o(t)$  are the respective input and output voltages of the driver. It can be seen (in Fig. 3) that  $i_d(t)$  is the difference between the drive current sourced by the pull-up network and that sunk by the pull-down network [22]

$$i_d(t) = i_{ds}^{pullup}(t) - i_{ds}^{pulldown}(t). \tag{7}$$

From transistor characteristics we know that given a constant drain-source voltage  $V_{ds}$ , the steady-state drain current  $I_{ds}$  is a monotonic increasing function of its gate-source voltage  $V_{gs}$ . We also know that the  $V_{gs}$  of the pull-up and the pull-down networks of a driver depends only on the gate input voltage  $v_i(t)$

$$V_{gs}^{pulldown} \propto v_i(t)$$

$V_{gs}^{pullup} \propto V_{dd} - v_i(t).$  (8)

Therefore, a decrease in the gate input voltage will affect the  $V_{gs}$  of the pull-up and pull-down network. From basic transistor current–voltage characteristics it follows that, for a *constant* output voltage, a *decrease* in the gate input voltage results in an increase (decrease) in the pull-up (down) current. Therefore, given a constant gate output voltage, the steady-state output drive current  $i_d(t)$  given by the difference between the pull-up and the pull-down current (7) also *increases*. In a dc analysis, it is easy to see that the above also holds for more complex gates or gates with skewed transistor stacks.

Similarly, from transistor characteristics we know that given a constant gate-source voltage, the steady-state drain current  $I_{ds}$  is a monotonic increasing function of its drain-source voltage  $V_{ds}$ . Therefore, a similar analysis leads to the observation that given a *constant* gate input voltage, a *decrease* in output voltage leads to an increase (decrease) in the pull-up (down) current, resulting in a corresponding *increase* in  $i_d(t)$ . Since the property relies only on the monotone behavior of the dc current  $I_{ds}$  with  $V_{ds}$  for metal-oxide semiconductor field-effect transistor transistors, it also holds for complex gates with transistor stacks and internal nodes. We sum up the above observations in the following property which relates the driver output current to driver input and output voltages.

*Property 1:* Given a specific input and output voltage, the magnitude of the drive current flowing out of a CMOS driver increases with a decrease in its input or output voltage.

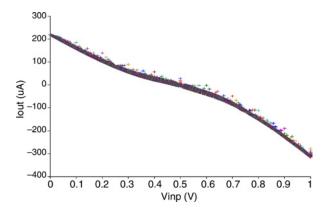

Strictly speaking, the above properties may not hold true during the entire transition due to the effect of Miller capacitance, especially if the driver input transitions very rapidly. In order to quantify the impact of Miller current, in Fig. 4 we plot the transient output current sourced by a CMOS inverter gate as a function of its input voltage. All simulations were performed on a typical (1X) inverter gate with fanout of four loading in 65 nm technology node using the HSPICE circuit simulator. The output voltage of the gate was held at a dc value

Fig. 4. HSPICE generated plot of driver output current versus input voltage for different input transitions.

of 0.5 virtual device driver (VDD) and the transition time of the gate input ramp signal was varied from 10 ps to 1 ns. In every simulation, the output current sourced (which includes the contribution of Miller current) was recorded. Since the Miller current is a function of the slew rate, we observe (in Fig. 4) a range of output current values for the same input voltage. However, it can be noted that the spread in output current values is rather small which implies that the contribution of Miller current is rather small compared to that sourced by inverter driver. Also, the spread would shrink for bigger gates with larger dc output current values.

One can also note that the amount of Miller current strongly depends on the ratio of the Miller capacitance to the output load capacitance. However, delay-noise is significant only for those victim nets that are coupled to several aggressors and which therefore have substantial output loading. For such victim nets, as observed in [23], the Miller current is typically negligible when compared to driver current and Property 1 implicitly holds. Furthermore, the Miller current is significant only for very fast input transitions and influences only the initial part of the output transition [24] which is of lesser interest in noise analysis. We will now employ the above property of driver current and prove the latest victim-input alignment result.

## B. Worst-Case Victim Alignment

In this subsection, we prove by contradiction that when the victim net is coupled to a single aggressor, the latest victim transition bounds all possible victim transitions. We will extend the ideas developed in this subsection in Section V when we prove the above for the more general case of multiple aggressors.

Theorem 2: Given a nonlinear victim and aggressor driver and monotonic victim-driver input transitions, the victim transition obtained by aligning the victim-driver input transition at the latest input arrival time, bounds any other feasible victim transition.

*Proof:* Consider the victim-aggressor configuration shown in Fig. 3, where  $C_a$  denotes the output load capacitances of aggressor driver,  $C_c$  denotes the coupling capacitance and the victim drives a reduced RC  $\pi$  model load. The victim-driver input transition  $v_i^l(t)$  is aligned at the latest time point

in its timing window and  $v_i^e(t)$  is an arbitrary earlier victimdriver input transition. The corresponding victim *driver* output transitions are denoted by  $v_o^e(t)$  and  $v_o^l(t)$ , respectively. Our goal is to show that the latest victim transition  $v_o^l(t)$  bounds any early victim transition  $v_o^e(t)$ , expressed mathematically in (2). Without loss of generality, we assume rising victim and falling aggressor transitions. Since it is necessary to show that (2) holds for all feasible aggressor transitions, we arbitrarily select an aggressor input transition which can occur anywhere within its timing window. Due to coupling-noise the aggressor transitions  $a_o^e(t)$  and  $a_o^l(t)$ , corresponding to the early and late victim transitions, may be different even though the input transition is the same (i.e.,  $a_i^e(t) = a_i^l(t)$ ). We first present an outline of the proof as follows.

- Victim Response Analysis: Suppose that a later victim transition crosses an early victim transition. Then, at the cross over point, we obtain a necessary relationship between the corresponding noise currents by analyzing the rate of change of the victim response.

- 2) Aggressor Response Analysis: Next, using this relationship between noise currents and the fact that aggressor input transition is same for both the cases, we compare the relative magnitudes of aggressor driver currents and derive a necessary relationship between the aggressor responses.

- 3) Charge Conservation: We then analyze the charge accumulated across the coupling capacitance due to both the early and late victim transitions and show that the necessary relationship between aggressor responses cannot be satisfied.

We prove by contradiction that the later victim transition must always bound any earlier victim transition, or mathematically  $v_o^e(t) \ge v_o^l(t) \ \forall t$ .

1) Victim Response Analysis: We begin our proof by analyzing the response at the output of the victim-driver. Suppose, the converse is true and there exists a time when both the victim waveforms cross each other for the *first* time (as shown in Fig. 5)

$$v_o^e(\tau_v) = v_o^l(\tau_v). (9)$$

From definition, the late victim transition  $v_o^l(t)$  starts rising after the early transition  $v_o^e(t)$ . Therefore, if  $v_o^l(t)$  manages to cross  $v_o^e(t)$  at time  $\tau_v$ , then it means that  $v_o^l(t)$  must be rising at a faster rate that  $v_o^e(t)$  at the time instant  $\tau_v$

$$\frac{\partial v_o^l(t)}{\partial t} > \frac{\partial v_o^e(t)}{\partial t} \mid_{t=\tau_v} . \tag{10}$$

We know that the charging current flowing into the victim load  $C_v$  is given by  $i_{c,v}(t) = C_v \times \frac{\partial v_o(t)}{\partial t}$ . Using (10) we obtain the following relationship:

$$i_{c,v}^l(\tau_v) > i_{c,v}^e(\tau_v) \tag{11}$$

where  $i_{c,v}^e(t)$  and  $i_{c,v}^l(t)$  are the currents flowing into the victim load  $C_v$  corresponding to the early and late victim transitions  $v_o^e(t)$  and  $v_o^l(t)$ , respectively (see Fig. 3). At crossover time  $t = \tau_v$ , the output voltages of the victim-driver are equal. From the assumption of monotonic falling victim-driver input

Fig. 5. Late victim crossing the earlier waveform.

transitions, we also have the inequality  $v_i^e(t) \le v_i^l(t) \mid_{t=\tau_v}$ . It follows from Property 1 that the victim-driver sources a larger current in the case of an early victim transition as compared to the late victim transition

$$i_{d,v}^{e}(\tau_{v}) > i_{d,v}^{l}(\tau_{v}).$$

(12)

It can be proved that the following relationship holds (see *Appendix*) between the currents flowing into the victim load  $C_L$ :

$$i_{r,v}^{l}(\tau_{v}) > i_{r,v}^{e}(\tau_{v}).$$

(13)

We can combine the inequalities in (11)–(13) to obtain the following inequality:

$$i_{d,v}^{e}(\tau_{v}) - i_{c,v}^{e}(\tau_{v}) - i_{r,v}^{e}(\tau_{v}) > i_{d,v}^{l}(\tau_{v}) - i_{c,v}^{l}(\tau_{v}) - i_{c,v}^{l}(\tau_{v}).$$

$$(14)$$

Applying Kirchhoff's Current Law (KCL) at the victim node and rewriting (14) in terms of the corresponding noise currents flowing through the coupling capacitance  $C_c$ , we obtain

$$i_n^e(\tau_v) > i_n^l(\tau_v). \tag{15}$$

2) Aggressor Response Analysis: Using the information about the victim transitions, we obtain a relationship between the early and late aggressor waveforms. The noise current flowing through the coupling capacitance  $C_c$  can be expressed in terms of the rate of change of the voltage difference across its terminals. After plugging the expressions for noise current into (15), we obtain

$$C_c \times \frac{\partial \{v_o^e(t) - a_o^e(t)\}}{\partial t} > C_c \times \frac{\partial \{v_o^l(t) - a_o^l(t)\}}{\partial t} \mid_{t=\tau_v} (16)$$

where  $a_o^e(t)$  and  $a_o^l(t)$  are the corresponding early and late aggressor waveforms (see Fig. 3). Rearranging both sides of (16), we obtain

$$\frac{\partial \{a_o^l(t) - a_o^e(t)\}}{\partial t} > \frac{\partial \{v_o^l(t) - v_o^e(t)\}}{\partial t} \mid_{t = \tau_v} . \tag{17}$$

From (10) we know that, at crossover time  $\tau_v$ , the rate of change of the late victim transition  $v_o^l(t)$  is greater than that of  $v_o^e(t)$ . Therefore, the term on the right-hand side (RHS) of (17) must be greater than zero and we get the following inequality between the early and the late aggressor waveforms:

$$\frac{\partial a_o^l(t)}{\partial t} > \frac{\partial a_o^e(t)}{\partial t} \mid_{t=\tau_v} . \tag{18}$$

We now provide an *intuition* for the analytical results that have been obtained so far. Suppose,  $v_o^l(t)$  rises at a relatively faster rate and crosses  $v_o^e(t)$  at time  $\tau_v$ . This implies two things about the relative current magnitudes of the currents flowing at the time instant  $\tau_v$ . For the late victim transition  $v_o^l(t)$ : 1) the current sourced by the victim-driver is less; and 2) the charging current flowing into the interconnect load is more, as compared to the early victim transition  $v_a^e(t)$ . Since the current sourced from the victim-driver equals the sum of the noise current and the charging load current, at time  $\tau_v$ , the noise current must be less for the later victim transition. Also, the noise current depends on the rate of change of the voltage difference across the coupling capacitance. At time  $\tau_v$ , the rate of change of the later victim transition is more. Therefore, the relationship among the noise currents demands that the rate of change of  $a_o^l(t)$  be less than that of  $a_o^e(t)$ . Note that the aggressor has falling output transitions. Therefore, both the derivative terms in (18) are negative in magnitude and early aggressor  $a_o^e(t)$ falls more rapidly than  $a_a^l(t)$ .

The discharging current of the aggressor interconnect load is given by

$$i_{c,a}(t) = -C_a \times \frac{\partial a_o(t)}{\partial t}.$$

(19)

The negative sign in the above expression is due to the convention followed that the load current is flowing out of the load capacitance  $C_a$  (see Fig. 3). Using (19) in (18), we obtain the following inequality between the early and late aggressor interconnect load currents:

$$i_{c,a}^{e}(\tau_{v}) > i_{c,a}^{l}(\tau_{v}).$$

(20)

Adding (20) and (15) together and applying KCL at the aggressor node, we obtain the following inequality among the aggressor driver currents:

$$i_{d,q}^{e}(\tau_{v}) > i_{d,q}^{l}(\tau_{v}). \tag{21}$$

Since the aggressor input transitions are the same in both cases, (i.e.,  $a_i^e(t) = a_i^l(t)$ ), the gate voltages of the aggressor driver are equal. Now, if the aggressor driver currents differ according to (21), then from *Property* 1 it follows that the output drain voltages of the aggressor must have the following relationship:

$$a_o^e(\tau_v) > a_o^l(\tau_v). (22)$$

To summarize, we obtain two necessary conditions on the aggressor waveforms at time  $\tau_v$ , that is  $a_o^l(t)$  must be lower than  $a_o^e(t)$  (22) and it must also transition at a slower rate (18).

3) Charge Conservation Analysis: At this point we will analyze the relationships between the driver current that is sunk by the aggressor driver in both cases. To do that, we need to define a time interval during which we compute the amount of charge sunk by aggressor driver. It follows from (22) that there must be a time  $\tau_a: 0 \le \tau_a < \tau_v$  where the early and late aggressor transitions intersect each other (see Fig. 5) that is

$$a_o^e(\tau_a) = a_o^l(\tau_a). (23)$$

If the late aggressor transition  $a_o^l(t)$  is always less than  $a_o^e(t)$  (as shown by the dotted waveform), then we choose  $\tau_a = 0$ . Instead, if  $a_o^l(t)$  and  $a_o^e(t)$  have multiple crossovers before time  $\tau_v$ , then we choose  $\tau_a$  to be the time at which the *latest* crossover occurs between the aggressor transitions. The boundary conditions on the victim–aggressor transitions in the interval  $[\tau_a, \tau_v]$  are as follows (as shown in Fig. 5):

$$a_{o}^{e}(\tau_{a}) = a_{o}^{l}(\tau_{a}), \quad a_{o}^{e}(\tau_{v}) > a_{o}^{l}(\tau_{v})$$

$$v_{o}^{e}(\tau_{a}) > v_{o}^{l}(\tau_{a}), \quad v_{o}^{e}(\tau_{v}) = v_{o}^{l}(\tau_{v}). \tag{24}$$

Since we chose  $\tau_a$  to be the latest occurring crossover time of aggressor transitions before  $\tau_v$ , we obtain the following monotonic relationship between the aggressor transitions:

$$a_o^e(t) > a_o^l(t) \quad \forall t \in (\tau_a, \tau_v).$$

(25)

Recall that the input to the aggressor driver is the same in both cases. From *Property* 1 and (25), it follows that the current sunk by the aggressor driver in the time interval is always greater in the early case, i.e.,

$$i_{d,a}^e(t) > i_{d,a}^l(t) \quad \forall t \in (\tau_a, \tau_v).$$

(26)

Integrating the above, we obtain the inequality between the total charge sunk by the aggressor driver  $Q_d^e$  and  $Q_d^l$ , respectively

$$\int_{\tau_a}^{\tau_v} i_{d,a}^e(t) \cdot dt > \int_{\tau_a}^{\tau_v} i_{d,a}^l(t) \cdot dt$$

$$\implies Q_d^e > Q_d^l.$$

(27)

We now analyze the relationships between the integrals of the noise current  $i_n(t)$  and the load current  $i_{v,a}(t)$  flowing into the aggressor in the time interval  $(\tau_a, \tau_v)$ . As both integrals are state functions they do not depend on the integration path but only depend on the voltage values at the boundaries of the interval  $(\tau_a, \tau_v)$ . The integral of load current  $Q_{c,a}^e$  for the early victim transition is

$$Q_{c,a}^{e} = \int_{\tau_{a}}^{\tau_{v}} i_{c,a}^{e}(t) \cdot dt$$

$$= -C_{a} \times \{a_{o}^{e}(\tau_{v}) - a_{o}^{e}(\tau_{a})\}$$

(28)

and similarly the integral of noise current  $Q_n^e$  is given by

$$Q_n^e = \int_{\tau_a}^{\tau_v} i_n^e(t) \cdot dt$$

=  $C_c \times \{ v_o^e(\tau_v) - v_o^e(\tau_a) + a_o^e(\tau_a) - a_o^e(\tau_v) \}.$  (29)

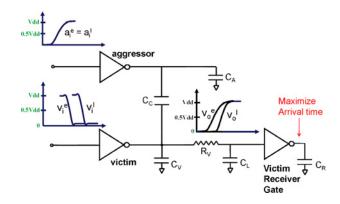

Fig. 6. Maximize victim receiver output arrival time.

Similarly, we can derive the integral of the load current  $Q_{c,a}^l$  and the integral of the noise current  $Q_n^l$  for the late victim transition. After plugging in the boundary values from (24), we obtain the following relationship:

$$Q_{c,a}^{l} > Q_{c,a}^{e} \quad and \quad Q_{n}^{l} > Q_{n}^{e}.$$

(30)

Adding both inequalities in (30) and applying KCL on the aggressor node, we obtain the following inequality:

$$Q_d^l > Q_d^e (31)$$

which contradicts the necessary condition (27). This proves that victim transition  $v_o^e(t)$  can never cross  $v_o^l(t)$  and the latest victim arrival time occurs only when the victim input is aligned at its latest input arrival time.

#### C. Worst-Case Victim Receiver Output Alignment

In this paper, we have focused on finding the victimdriver input transition which results in the latest victim arrival time. However, as reported in [19], the true objective of delay-noise analysis is not to maximize the victim arrival time, but to maximize the output arrival time of the victim receiver gate (see Fig. 6). In this subsection, we show that the victim alignment at the latest point in its timing window, also maximizes the victim receiver output arrival time. In other words, the latest victim transition bounds any earlier victim transition.

Theorem 3: Given nonlinear victim-aggressor driver models and monotonic victim-driver input transitions, alignment of the victim-driver input transition at the latest input arrival time results in the latest arrival time at the victim receiver output.

*Proof:* Given nonlinear victim-aggressor drivers, it was proved that the early  $(v_o^e(t))$  and late  $(v_o^l(t))$  victim waveforms do not cross each other. Hence, the latest victim transition always bounds the early victim transition. It can be noted that we have exactly the same setup at the input of the victim *receiver* gate as we had for the victim *driver* gate, i.e., the victim receiver gate input  $v_o^l(t)$  bounds  $v_o^e(t)$ . Therefore, using Property 1, we can compare the relative magnitudes of the driver output current sourced in both cases. Repeating the exact same analysis (performed on the victim-driver) for the victim receiver gate we can arrive at the desired result

Fig. 7. Victim net coupled to multiple aggressors.

which claims that late victim receiver output transition will bound any earlier victim transition.

From the above theorem, it follows that the latest victim-driver input transition leads to the latest victim receiver output transition. Hence, the latest alignment result holds for a system having two single stage gates cascaded together (i.e., victim-driver and receiver). Therefore, it is easy to see that a similar analysis extends easily for the case when the victim-drivers are complex multistage gates (e.g., AND/XOR).

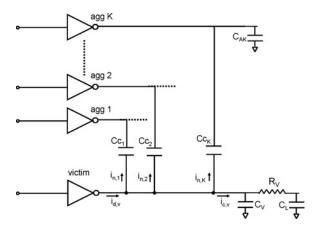

#### V. VICTIM ALIGNMENT FOR MULTIPLE AGGRESSORS

In the previous section, we showed that the latest victim alignment result holds for the case when the victim was coupled to a single aggressor. However, in reality the victim net is usually coupled to more than one aggressors. Therefore, it is natural to ask whether the latest victim alignment result also holds for the case when the victim is coupled to multiple aggressors. In this section, we state and prove the following theorem.

Theorem 4: Given nonlinear victim-aggressor drivers and multiple aggressors with coupling capacitances coupled to the victim-driver output, the victim transition obtained when its input transition occurs at the latest input arrival time bounds any other victim transition.

*Proof:* Suppose, there are K aggressors coupled to the victim-driver output and the noise current flowing into the  $k^{th}$  aggressor be given by  $i_{n,k}(t)$  (as shown in Fig. 7). The above lumped interconnect model can be obtained by applying model-order reduction techniques to the distributed victim-interconnect load. We perform the *victim response analysis*, in which we first assume that both the early and late victim-driver output waveforms cross each other at time  $\tau_v$ . Now, the total noise current flowing out of the victim interconnect will be the cumulative sum of the individual noise currents flowing through each coupling capacitance. Therefore, the current flowing into the victim interconnect  $(i_{c,v}(t))$  can be obtained by the subtracting all the noise currents from victim-driver current  $(i_{d,v}(t))$

$$i_{c,v}(t) = i_{d,v}(t) - \sum_{k=1}^{k=K} i_{n,k}(t).$$

(32)

Fig. 8. Representative experimental circuit with the victim net coupled to two aggressor nets.

We substitute the expression of  $i_{c,v}(t)$  derived above into (11) and (12) to obtain the following inequality between the cumulative sum of the early and late noise currents at crossover time  $\tau_v$ :

$$\sum_{k=1}^{k=K} i_{n,k}^{e}(\tau_{v}) > \sum_{k=1}^{k=K} i_{n,k}^{l}(\tau_{v}).$$

(33)

Note that the above inequality between the cumulative early and late noise currents is a necessary condition for a crossover to occur between the early and the late victim transitions at time  $\tau_v$ . It is easy to see that for the above inequality (33) to hold, there must be at *least* one aggressor, say  $a_m$ , whose noise currents satisfies the following relationship:

$$i_{n,m}^{e}(\tau_{v}) > i_{n,m}^{l}(\tau_{v}).$$

(34)

The analysis that follows is exactly the same as that for the single aggressor case described in the previous section. Performing the *aggressor response analysis* on  $a_m$ , we obtain the following relationships between the early and late aggressor waveforms  $a_{o,k}^e(t)$  and  $a_{o,k}^l(t)$  at the crossover time  $(\tau_v)$ :

$$a_{o,m}^{e}(\tau_{v}) > a_{o,m}^{l}(\tau_{v}).$$

(35)

Proceeding in a similar fashion, we identify  $\tau_{a,m}$  which is the latest crossover time between aggressor waveforms  $a_{o,m}^e$  and  $a_{o,m}^l$  occurring before the time  $\tau_v$ . Finally, we perform the *charge conservation analysis* on aggressor  $a_m$ . We compare the magnitude of the total charge sunk through the aggressor driver in the early and late case within the time interval  $(\tau_{a,m}, \tau_v)$  and obtain the desired contradiction.

It was shown that even when the victim is coupled to multiple aggressors, the early and late victim transitions can never cross each other. Therefore, the latest victim arrival time occurs only when its input is aligned at the latest point in its timing window. Note that while computing the worst-case victim arrival time for a given victim—aggressor configuration, we account for only the mutual interaction between the victim and the aggressor transitions. This is because, in the delaynoise analysis, the mutual interaction between the aggressor transitions are captured during the global iterations of the delay-noise computation algorithm.

Fig. 9. Victim waveform obtained by sweeping victim-driver input waveform.

#### VI. RESULTS

In this section, we look at experimental results which confirm the efficacy of our proposed approach. We perform HSPICE simulations which validate our claim that the latest victim-driver input transition will maximize the victim arrival time. Later we also compare the proposed approach with existing heuristic techniques and report the runtime improvement over the existing approaches.

### A. HSPICE Simulations

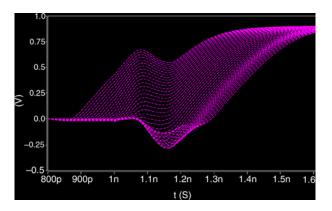

In order to validate the latest alignment result for nonlinear driver models, we perform HSPICE simulations on the victim-aggressor coupled circuit (shown in Fig. 8) in the 65 nm technology node. In reality the representative circuit has several variable parameters such as the victim-aggressor driver strength, the victim-aggressor driver input transition slew rates, the victim-aggressor interconnect length and spacing, the magnitude of the victim receiver load, etc. In order to adequately sample the above mentioned parameter space, we perform a total of about 4096 simulations by randomly sampling the parameter values within the range as shown in Table I. In each simulation, the alignment of both aggressordriver input transitions was arbitrarily selected within their timing windows which were 300 ps wide each. The alignment of victim-driver input transition is now swept within its timing window and the victim response was obtained using the HSPICE simulator. We show, in Fig. 9, the victim response obtained in one of the simulations in which the couplingnoise bump was greater than 25% VDD. It can be seen that none of the victim transitions intersect with each other, validating the result that the latest victim-driver input alignment results in the worst-case victim arrival time. The above result was verified to hold true across all HSPICE simulations on the experimental circuits obtained by randomly sweeping the circuit parameters.

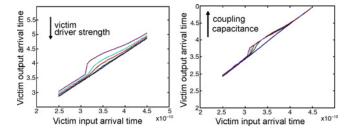

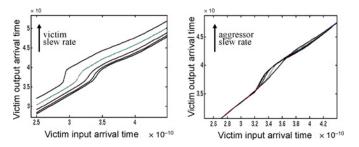

We also performed HSPICE simulations on the single aggressor case shown in Fig. 3. In Fig. 10, we show the plots of the victim arrival times obtained by sweeping the victim-input arrival time for different values of the victim-driver strength and coupling capacitances. Fig. 11 shows a similar plot, where we vary the input slew rates of the victim and aggressor drivers. As expected, it can be seen that all plots

Fig. 10. HSPICE plots of victim arrival time versus victim-driver input arrival time for different victim-drivers and coupling capacitances.

Fig. 11. HSPICE plots of victim arrival time versus victim-driver input arrival time for different victim and aggressor input-slew rates.

are monotonically increasing, in agreement with our claim that the latest victim-driver input transition results in latest victim arrival time.

To further illustrate the latest victim alignment result presented in Section IV, we show in Fig. 12 the output responses generated in HSPICE for a "pathological" victim-aggressor configuration. We fix the aggressor input arrival time and sweep the input skew by shifting the victim-driver input transition to the right. Note that as we delay the victimdriver input transition, the aggressor transition initially starts to switch faster. This is because the Miller effect due to the switching of the victim is delayed since its starts switching later. Also, due to the noise coupled from the aggressor, the delayed victim transition starts from a voltage below zero. This increases the drain-source voltage of the pull-up network of the victim-driver and the victim waveform starts rising rapidly. However, as the victim transition starts approaching an earlier transition, the corresponding aggressor transitions cross each other (see Fig. 12). This violates the necessary condition of (22) and the victim transitions never cross each other.

In our final example, we consider the circuit shown in Fig. 3 with a strong aggressor coupled to the victim. In this example, the aggressor transition results in a very large coupling-noise pulse on the victim as shown in Fig. 13. As we shift the arrival time of the victim-driver input transition closer to the aggressor transition, it can be observed that the noise pulse peak increases. The reason for the increases in the noise peak is the increase in the victim-driver output resistance with an increases in the overlap between aggressor—victim transitions. This effect is often referred to as "driver-weakening" and it leads to an increase in the noise pulse peak with an increase in the overlap between aggressor—victim transitions. However, it can be seen that inspite of driver-weakening, a later victim transition always bounds an earlier victim transition. Hence,

Coupling Scaling Factor (Cc/Ca)

| Parameters                       | Range of Values                         |  |  |

|----------------------------------|-----------------------------------------|--|--|

| Victim-Driver Strength           | 1X, 2X, 4X, 6X, 10X, 12X, 16X, 20X, 24X |  |  |

| Victim-Driver Input Slew (ps)    | (10, 200)                               |  |  |

| Victim Interconnect Length (μm)  | (5, 200)                                |  |  |

| Victim Receiver Load (fF)        | (1, 200)                                |  |  |

| Aggressor Driver Strength        | 1X, 2X, 4X, 6X, 10X, 12X, 16X, 20X, 24X |  |  |

| Aggressor Driver Input Slew (ps) | (10, 200)                               |  |  |

$\label{eq:table_interpolation} \textbf{TABLE I}$  Parameters of the Experimental Victim – Aggressor Circuit

Fig. 12. HSPICE simulation plots showing the victim-aggressor transitions.

Fig. 13. Noise peak as a function of victim transition.

as expected, this example illustrates that even when there is a significant amount of coupling-noise, the latest victim-driver input alignment always results in latest victim arrival time.

#### B. Delay-Noise Analysis

A prototype static noise analysis tool was implemented in C++ programming language which uses linear driver models to perform the noise analysis. This tool uses the proposed approach of aligning the victim transition at the latest point in its timing window and its efficacy was tested on the mobile communication and networking center of excellence (MCNC) benchmark circuits. These benchmark circuits were synthesized in 130 nm technology and then placed-and-routed by using a commercial APR tool. A commercial parasitic

Fig. 14. Charging the victim RC load.

(0.5, 2)

extraction tool was used to extract the distributed interconnect RC values and then noise analysis was performed using industrial timing libraries. All experiments were run on a 1 GHz SUN machine with 4 GB of memory.

A summary of the experimental results obtained for MCNC benchmark circuits is listed in Table I. The details of all circuits are given in the first four columns, while the results of the proposed approach are given in the final four columns. In column 4, we report the worst-case graph delay of the circuit. To obtain the worst-case victim arrival time, we align the victim-driver input transition at the latest point in its timing window. The worst-case aggressor alignment is computed such that it maximizes the 50% crossover time of the victim transition [25]. The fact that we no longer need to search for the victim alignment within the victim timing window simplifies the overall alignment algorithm and results in a speedup of the noise analysis engine. We compare the latest victim alignment approach with that proposed in [18], where victim alignment is enumerated at the end points of victim and the aggressor timing windows. For example, in Fig. 2 this approach requires the alignment of the victim transition at four different arrival times  $t_1$ ,  $t_2$ ,  $t_3$ , and  $t_v$ . The worst-case alignment of aggressors was found for each victim alignment and finally the victim-aggressor alignment which results in the maximum output arrival time was reported. It was observed that the delay-noise values reported by both approaches were identical. This confirms the fact that victim alignment at the latest point in its timing window is optimal and an enumeration of victim alignment within its timing window is not necessary to maximize victim arrival time. Since our proposed approach requires only a single victim alignment, an average speedup of 4.3X was achieved over [18] on benchmark circuits.

With the victim-input alignment fixed at the end points of its timing window, the number of aggressors that can now align with the victim transition are reduced substantially. For

| Circuit Name | # of Nets | # of Agg | Circuit Delay (in ns) | # of Agg Pruned | % of Agg Pruned | Run Time (in s) | Speedup |

|--------------|-----------|----------|-----------------------|-----------------|-----------------|-----------------|---------|

| i1           | 46        | 232      | 0.546                 | 103             | 44.39           | 0.01            | 2.74    |

| i2           | 221       | 706      | 0.743                 | 324             | 45.89           | 0.02            | 2.46    |

| i3           | 126       | 551      | 0.529                 | 281             | 50.99           | 0.02            | 3.12    |

| i4           | 230       | 1181     | 0.801                 | 610             | 51.65           | 0.02            | 3.56    |

| i5           | 138       | 1835     | 1.212                 | 794             | 43.27           | 0.04            | 4.88    |

| i6           | 668       | 7298     | 1.045                 | 3066            | 42.01           | 0.14            | 5.15    |

| i7           | 870       | 9605     | 1.124                 | 4925            | 51.27           | 0.15            | 6.19    |

| i8           | 1528      | 10235    | 1.636                 | 5436            | 53.11           | 0.21            | 5.32    |

| i9           | 955       | 14140    | 1.841                 | 6789            | 48.02           | 0.33            | 6.91    |

| i10          | 3155      | 18318    | 3.089                 | 8744            | 47.73           | 0.45            | 3.21    |

TABLE II

RESULTS FOR THE PROPOSED LATEST VICTIM ALIGNMENT APPROACH

example, in Fig. 2 only aggressor  $a_3$  can inject noise onto the victim transition. All aggressors which can no longer inject noise onto the fixed victim transition (e.g., aggressors  $a_{1-2}$  in Fig. 2) can be safely ignored in noise analysis. In Table I, it can be seen that almost half of the total number of aggressors in the circuit can be eliminated from delay-noise analysis in this manner. This results in further a speedup of the overall noise analysis engine. We can also note that the maximum speedup is achieved for the circuit i9 which has the largest number of aggressors per victim net (approximately 14). Hence, for larger industrial circuits with several aggressors nets per victim, large speedups can be achieved.

## VII. CONCLUSION

In this paper, we prove that the latest victim arrival time occurs only when its input transition is aligned at the latest point in its timing window. While the proof is fairly straightforward for linear drivers, it is nontrivial for nonlinear CMOS drivers. The result in this paper obviates the need for enumerating the victim-input timing window in delay-noise analysis. Consequently, the victim-aggressor alignment problem is simplified and its complexity is significantly reduced. Although this result has been observed empirically in the industry, this is the first paper which analytically shows that the result holds for both linear and nonlinear drivers. We show that significant speedup can be achieved on benchmark circuits over existing heuristic solutions without incurring any loss of accuracy.

## APPENDIX

Inequality Between Victim Load Currents

In this section, we prove the following inequality between the instantaneous load currents at crossover time  $\tau_v$ :

$$i_{r,v}^l(\tau_v) > i_{r,v}^e(\tau_v) \tag{36}$$

where  $i_{r,v}^e(t)$  and  $i_{r,v}^l(t)$  are the currents (see Fig. 3) flowing into the victim load  $(R_vC_L)^2$  corresponding to the early  $(v_o^e(t))$  and late  $(v_o^l(t))$  victim-driver output transitions, respectively. The

current  $i_{r,v}^e(t)$  is a function of the voltage differences across the terminals of the resistance  $R_v$ , i.e.,

$$i_{r,v}^{e}(t) = \frac{v_o^{e}(t) - v_L^{e}(t)}{R_v}$$

where  $v_L^{e}(t)$  and  $v_L^{l}(t)$  are the early and late voltages across

where  $v_L^e(t)$  and  $v_L^l(t)$  are the early and late voltages across the load capacitance  $C_L$ . Subtracting the instantaneous early and late victim load currents at the crossover time instant  $\tau_v$

$$i_{r,v}^{l}(\tau_{v}) - i_{r,v}^{e}(\tau_{v}) = \frac{\{v_{o}^{l}(\tau_{v}) - v_{L}^{l}(\tau_{v})\} - \{v_{o}^{e}(\tau_{v}) - v_{L}^{e}(\tau_{v})\}}{R_{v}}.$$

(38)

However by definition of crossover time  $\tau_v$ , the early and late victim waveforms have the same value at crossover time  $\tau_v$  (i.e.,  $v_o^l(\tau_v) = v_o^e(\tau_v)$ ). Hence, the difference between instantaneous load currents (38) becomes

$$i_{r,v}^{l}(\tau_{v}) - i_{r,v}^{e}(\tau_{v}) = \frac{v_{L}^{e}(\tau_{v}) - v_{L}^{l}(\tau_{v})}{R_{v}}.$$

(39)

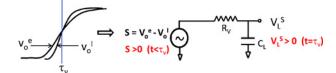

Using linear superposition principle, we will prove that the term on the RHS of (39) is positive. In Fig. 14, we can see the victim  $R_vC_L$  load being charged by a voltage source S(t)

$$S(t) = v_o^e(t) - v_o^l(t). (40)$$

obtained by subtracting the late victim  $v_o^l(t)$  from the early victim  $v_o^e(t)$ . From definition,  $\tau_v$  is the first time when the victim waveforms cross each other and therefore

$$S(t) \geq 0, \quad \forall t \leq \tau_v.$$

(41)

During the time  $t < \tau_v$ , the  $R_v C_L$  load is being charged by a nonnegative voltage source S(t). Therefore, at crossover time  $\tau_v$ , the load capacitance will have accumulated a net positive charge. Therefore

$$V_I^S(\tau_v) > 0. (42)$$

Using linear superposition principle, we can rewrite the above equation as

$$v_I^e(\tau_v) - v_I^l(\tau_v) > 0.$$

(43)

Finally, using (43) in (39), we establish the inequality between the instantaneous load currents

$$i_{r,v}^l(t) - i_{r,v}^e(t) > 0.$$

(44)

Note that the above inequality between the load current also holds when the victim drives a distributed RC load.

<sup>&</sup>lt;sup>2</sup>Note that a similar analysis may not hold with an *RLC* interconnect load.

#### REFERENCES

- [1] D. Sinha and H. Zhou, "Statistical timing analysis with coupling," *IEEE Trans. Computer-Aided Design Integr. Circuits Syst.*, vol. 25, no. 12, pp. 524–531, Dec. 2006.

- [2] K. L. Shepard and V. Narayanan, "Noise in deep submicron digital design," in *Proc. IEEE/ACM Int. Conf. Comput.-Aided Des.*, San Jose, CA, Nov. 10–14, 1996, pp. 524–531.

- [3] K. L. Shepard, V. Narayanan, P. C. Elmendorf, and G. Zheng, "Global harmony: Coupled noise analysis for full-chip RC interconnect networks," in *Proc. Int. Conf. Computer-Aided Des.*, San Jose, CA, 1997, pp. 139–146.

- [4] S. S. Sapatnekar, "A timing model incorporating the effect of crosstalk on delay and its application to optimal channel routing," *IEEE Trans. Computer-Aided Design Integr. Circuits Syst.*, vol. 19, no. 5, pp. 550–559, May 2000.

- [5] R. Arunachalam, K. Rajagopal, and L. T. Pilleggi, "Taco: Timing analysis with coupling," in *Proc. Conf. Des. Automat.*, Los Angeles, CA, 2000, pp. 266–269.

- [6] H. Zhou, N. Shenoy, and W. Nicholls, "Timing analysis with crosstalk is a fixpoint on a complete lattice," in *Proc. 38th Annu. Design Automat. Conf.*, Las Vegas, NV, 2001, pp. 714–719.

- [7] S. H. Choi, F. Dartu, and K. Roy, "Timed pattern generation for noise-on-delay calculation," in *Proc. 39th Annu. Design Automat. Conf.*, New Orleans, LA, 2002, pp. 870–873.

- [8] L. H. Chen and M. Sadowska, "Aggressor alignment for worst-case coupling noise," in *Proc. Int. Symp. Phys. Design*, San Diego, CA, 2000, pp. 48–54.

- [9] P. Chen, D. A. Kirkpatrick, and K. Keutzer, "Miller factor for gate-level coupling delay calculation," in *Proc. IEEE/ACM Int. Conf. Computer-Aided Design*, San Jose, CA, 1998, pp. 68–73.

- [10] A. B. Kahng, S. Muddu, and E. Sarto, "On switch factor based analysis of coupled RC interconnects," in *Proc. 37th Design Automat. Conf.*, 2000, pp. 79–84.

- [11] J. M. Wang, O. Hafiz, and P. Chen, "A non-iterative model for switching window computation with crosstalk noise," in *Proc. Asia South Pacific Design Automat Conf.*, Pacifico Yokohama, Yokohama, Japan, 2004, pp. 846–851.

- [12] Y. Sasaki and G. De Micheli, "Crosstalk delay analysis using relative window method," in *Proc. 12th Annu. IEEE Int. Applicat-Specified Integr. Circuit/Syst.-Chip Conf.*, Washington D.C., 1999, pp. 9–13.

- [13] Y. Sasaki and K. Yano, "Multiaggressor relative window method for timing analysis including crosstalk delay degradation," in *Proc. IEEE Custom Integr. Circuits Conf.*, Orlando, FL, 2000, pp. 495–498.

- [14] T. Sato, Y. Cao, D. Sylvester, and C. Hu, "Characterization of interconnect coupling noise using in-situ delay change curve measurements," in *Proc. Application-Specified Integr. Circuit/Syst.-Chip*, 2000, pp. 321–325

- [15] K. Agarwal, T. Sato, Y. Cao, D. Sylvester, and C. Hu, "Efficient generation of delay change curves for noise-aware static timing analysis," in *Proc. Asia South Pacific Design Automat. Conf.*, 2004, pp. 342–348.

- [16] J. F. Croix and D. F. Wong, "Blade and razor: Cell and interconnect delay analysis," in *Proc. 40th Design Autom. Conf.*, Anaheim, CA, 2003, pp. 386–389.

- [17] T. Xiao and M. Sadowska, "Worst delay estimation in crosstalk aware static timing analysis," in *Proc. Int. Conf Comput. Design*, Austin, TX, 2000, pp. 115–120.

- [18] M. R. Becer, V. Zolotov, R. Panda, A. Grinshpon, I. Algor, R. Levy, and C. Oh, "Pessimism reduction in crosstalk noise aware STA." in *Proc. Int. Conf. Computer-Aided Design*, San Jose, CA, 2005, pp. 954–961.

- [19] I. Keller, K. Tseng, and N. Verghese, "A robust cell-level crosstalk delay change analysis," in *Proc. Int. Conf. Computer-Aided Design*, 2004, pp. 147–154.

- [20] S. Sirichotiyakul, D. Blaauw, C. Oh, R. Levy, V. Zolotov, and J. Zuo, "Driver modeling and alignment for worst-case delay-noise," in *Proc. Design Automat. Conf.*, 2001, pp. 720–725.

- [21] R. Levy, D. Blaauw, G. Braca, A. Dasgupta, A. Griashpon, C. Oh, B. Orshay, S. Sirichotiyakul, and V. Zolotov, "Clarinet: A noise analysis tool for deep submicron design," in *Proc. 37th Design Automat. Conf.*, 2000, pp. 233–238.

- [22] V. Raghavan and R. A. Rohrer, "A new nonlinear driver model for interconnect analysis," in *Proc. 28th ACM/IEEE Design Automat. Conf.*, 1991, pp. 561–566.

- [23] A. Goel and S. Vrudhula, "Current source based standard cell model for accurate signal integrity and timing analysis," in *Proc. Conf. Design*, *Automat. Test Eur.*, Munich, Germany, 2008, pp. 574–579.

- [24] S. Raja, F. Varadi, M. Becer, and J. Geada, "Transistor level gate modeling for accurate and fast timing, noise, and power analysis," in *Proc. 45th Annu. Design Automat. Conf.*, Anaheim, CA, 2008, pp. 456– 461.

- [25] P. D. Gross, R. Arunachalam, K. Rajagopal, and L. T. Pileggi, "Determination of worst-case aggressor alignment for delay calculation," in Proc. Int. Conf. Computer-Aided Design, 1998, pp. 212–219.

Ravikishore Gandikota received the B.Tech. degree in electronics and electrical communication engineering from Indian Institute of Technology Kharagpur, Kharagpur, India, in 2005, and the M.S. and Ph.D. degrees in electrical engineering from the Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, in 2007 and 2009, respectively.

He was a Summer Intern with Intel Corporation, Bangalore, India, in 2004, with Freescale Semiconductors, Austin, TX, in 2007, and with Synopsys,

Mountain View, CA, in 2008. His research interests include signal integrity issues, crosstalk noise, static and statistical timing analysis, and variability aware circuit design techniques.

Kaviraj Chopra received the B.E. degree in instrumentation and control from Gujarat University, Ahmedabad, India, in 2001, the M.S. degree in electrical and computer engineering from the University of Arizona, Tucson, in 2004, and the Ph.D. degree in computer science from the Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, in 2008

He was with the National Optical and Astronomical Observatory, Tucson, AZ, during the winter and summer of 2003. He was a Summer Intern with IBM

Corporation, Austin, TX, in 2005, and with Synopsys, Mountain View, CA, in 2006. He is currently working as a PnR Engineer with Mentor Graphics, San Jose, CA.

**David Blaauw** (M'00–SM'07) received the B.S. degree in physics and computer science from Duke University, Durham, NC, in 1986, the M.S. and Ph.D. degrees in computer science from the University of Illinois, Urbana, in 1988 and 1991, respectively.

Until August 2001, he was with Motorola, Inc., Austin, TX, as a Manager of the High-Performance Design Technology Group. Since August 2001, he has been on the Faculty of the Department of Electrical Engineering and Computer Science, University

of Michigan, Ann Arbor, where he is currently a Professor. His work has focused on very large-scale integration design with particular emphasis on ultralow power and high-performance design.

Dr. Blaauw was the Technical Program Chair and General Chair for the International Symposium on Low Power Electronic and Design, as well as the Technical Program Co-Chair and Member of the Executive Committee the ACM/IEEE Design Automation Conference. He is currently a Member of the International Solid-State Circuits Conference Technical Program Committee

**Dennis Sylvester** (S'95–M'00–SM'04) received the B.S. degree in electrical engineering (summa cum laude) from the University of Michigan, Ann Arbor, in 1995, and the M.S. and Ph.D. degrees in electrical engineering from the University of California, Berkeley, in 1997 and 1999, respectively.

Currently, he is an Associate Professor with the Department of Electrical Engineering, University of Michigan, Ann Arbor. He previously held Research Staff positions with the Advanced Technology Group, Synopsys, Mountain View, CA, and with

Hewlett-Packard Laboratories, Palo Alto, CA. He also serves as a Consultant and Technical Advisory Board Member for several electronic design

automation firms in these areas. He has published numerous articles along with one book and several book chapters in his field of research, which includes low-power circuit design and design automation techniques, design-for-manufacturability, and on-chip interconnect modeling.

Dr. Sylvester was a recipient of the National Science Foundation CAREER Award, the 2000 Beatrice Winner Award at the International Solid-State Circuits Conference, the 2004 IBM Faculty Award, several Best Paper Awards and nominations, the ACM SIGDA Outstanding New Faculty Award, the 1938E Award from the College of Engineering for teaching and mentoring, and the Henry Russel Award, which is the highest award given to Faculty at the University of Michigan. He has served on the Technical Program Committee of numerous design automation and circuit design conferences, and was the General Chair of the 2003 ACM/IEEE System-Level Interconnect Prediction Workshop and the 2005 ACM/IEEE Workshop on Timing Issues in the Synthesis and Specification of Digital Systems. He is currently an Associate Editor for the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION SYSTEMS. He also helped to define the circuit and physical design roadmap as a Member of the International Technology Roadmap for Semiconductors, U.S. Design Technology Working Group from 2001 to 2003. He is a Member of ACM, American Society of Engineering Education, and Eta Kappa Nu. His dissertation research was recognized with the 2000 David J. Sakrison Memorial Prize as the most outstanding research in the Department of Electrical Engineering and Computer Science, University of California, Berkeley.