EMIR New hire training » History » Revision 2

« Previous |

Revision 2/10

(diff)

| Next »

jun chen, 03/21/2025 11:46 PM

EMIR New hire training¶

Welcome on board, new hires!¶

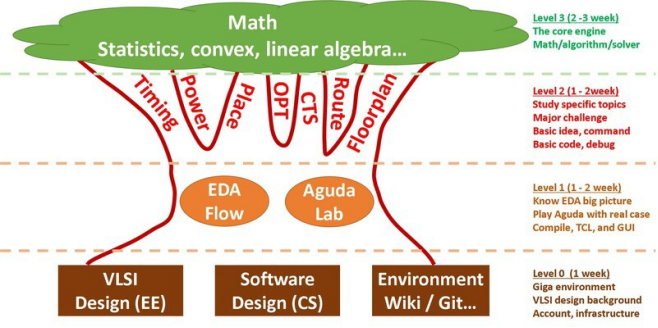

We provide a tree-like training plan for you.

Most of the materials are designed in self-driven study flavor.

Please check below expert-tree first, and start with level-0 lectures.

Good good study, day day up!

Level-0 Background and environment¶

On board environment setup.¶

- Check your environment before next step on_board_check_list.pptx

Note: if you can't find SH printer driver, use this: Win_x64.zip or ask IT for help - 员叩O叩 员叩O叩2021O.pdf 0 员叩O叩2023011O.pdf

- EMIR 叩叩叩叩 0000000000000000 (DD D田0出叩0叩程叩0叩D DD经叩叩叩加叩0叩有叩叩加D叩D叩0请叩看叩叩叩叩叩叩叩接叩

- IT new hire training: http://10.30.200.21:8088/attachments/3632

- Document templates (New version after 20220815) GIGA_VI_Standards

Refresh VLSI knowledge.¶

-

Step 1: Go through the briefing slide EDA_BG_Briefing.pptx Make sure you are familiar with fundamental terminologies. Try to answer the questions in the slides.

(Hint 1: most of the answer in this book CMOS_VLSI.part1.rarCMOS_VLSI.part2.rar )

(Hint 2: You can use FreePDK45_Giga.rar as standard cell library, and use Ngspice to setup transistor-level circuit simulation.) -

Step 2: Hand out your answers to tutor, you are welcomed to raise new questions to us.

-

Next step: EDA_Traveller

Get ready to survive in Linux world0 A quick start EDA journey.¶

- Please follow Survive_linux to learn how to survive in GIGA Linux environment.

- Please follow Setup_linux to setup / restore / reset your linux VNC development environment, and run quick start EDA.

- Checkout Quick_shell.docx, make sure you are familiar with Linux shell command...

- home directory and VNC upgrade procedure (2023/12/17)

Giga IT guide map.¶

800

Advanced C++ topic.¶

-

Giga uses make file to organize source code. Checkout tutorial Usage_of_Makefile.pptx (JiaXiao Qin, 2020/08/26)

-

Debug and profiling skills, please visit http://10.30.200.21:8088/projects/hongtu-emir/wiki/Debugging_and_profiling_tech (JiCun Li, 2020/08/26)

-

how to use lambda expression. Check tutorial lambda_expression.pptx (JiaXiao Qin, 2021/05/21)

-

Tcl usage and coding from scratch Tcl.hD叩叩叩pre_leping.pptx (LePing Wang, 2022/03/18)

-

Learn modern C++ features: https://github.com/changkun/modern-cpp-tutorial

Level-1 EDA flow and play with Aguda¶

The BIG picture of EDA flow and Aguda EDA lab {For new environment)¶

- Read through Verilog to manufacture lecture, so you can get the big picture of EDA flow, and play with a tiny chip case.

- Read through EMIR sign-off basics: SoCDDDDO叩D.docx (From DD谈加)

The BIG picture of Vulcan Power and VP manual {For new environment)¶

- Please check http://10.30.200.21:8088/projects/hongtu-emir/wiki/New_hire_training(PV_PE_AE) , "VP introduction" section.

- Please follow "D叩叩DO叩" on the main functions of VP

Level-2 Time to become EDA RD¶

( * DDDDDDDDDDDD make !!!! D00D bsub / vp_make / ag_make / cht_make * )

( * DDDDDDDDDDDD make !!!! D00D bsub / vp_make / ag_make / cht_make * )

( * DDDDDDDDDD git push!!!! DODD vp_commit 执D叩叩叩 00D00D vp_push / ag_push / cht_push * )

( * DDDDDDDDDD git push!!!! DODD vp_commit 执D叩叩叩 00D00D vp_push / ag_push / cht_push * )

( * □□□DD /rnd1/jchen/newhire_training/util_scripts *)

700

Development flow, an issue cycle¶

-

How to Create repository (建叩本叩DODD)

-

RD cycle flow check_in_flow_regression_new.pptx ,

Learn how to get issue, fix, test, verify, review, and submit change.

Run below script to see check-in guidance ( Thanks to 杜田D )

/rndl/llchen/newhire—training/util—scripts/vp—commit

-

About git:

Learn git within one hour (why rebase? how to merge, reset, revert?) git_in_one_hour.docx

Simple git flow introduction and some common issues when using git (contributed by 陈田奇) git_simple_intro.pptx Get used to git branch operation (contributed by 周田邦) https://learngitbranching.js.org/

Use gitk to trace changes and commits (you may also use gigacode diff) (contributed by 熊叩安) -

About regression and utility system

See details in http://10.30.200.21:8088/projects/hongtu-emir/wiki/VP_QA_(regression)_

The official Redmine issue flow: http://10.30.200.21:8088/projects/it-infrastructures/wiki/Redmine_User_Guide

Useful tools {under /rnd1/jchen/newhire_training/util_scripts )¶

vp_hello // show usage and help message

vp_newhire // setup environments during on-board day

vp_new // vp—checkout + vp—make check out code from server and build AG/VP/C日T

vp_checkout // check out latest code from gitlab server

vp_clean // clean up binary (make clean)

vp_make // build VP binary, or...

vp_make ir pow // will make ir and pow module as debug version

vp_make ir VERBOSE // will enable verbose message during compile

vp_make pow ta FORCE // will call a machine and force compile, if resource is limited

ag_make // build AG binary, or...

// usage is same as vp—make

cht_make // build CHT binary

// usage is same as vp—make

rs_make // build RS binary

vp_sync/ag_sync/cht_sync // get latest code from server, and refresh ctags

vp_sync_force // 髻 强伲merge conflict叩叩且叩正叩交叩

vp_regression // run VP regression suite under your client (M-ST do for functional check-in flow)

cht_regression // run C日T regression suite

ag_regression // run AG regression suite under your client (M-ST do for functional check-in flow)

ag—regression clean 髻 cleanup local regression data, same as "vp—regression clean"

vp—commit //print check-in flow guidance

vp—push // perform sync-up, AG/C日T/VP build, run simple check, and push your code to gitlab server

vp—revert // a simple guidance if you want to give-up change, or solve conflict...

ut—push // push changes for ut case, will do --rebase

VP—cut—build // how to build cut release to AF (commit id in etc/ci—log)

Note: If vp_sync or git pull failed with "You are not currently on a branch" try to use git checkout hongtu to recover branch info.

RD IDE related¶

xterm By ZhengYu

vim By JiCun

Speed-up vim By PengCheng, Dr. Liu

vscode By DanPing

Setup shell alias and git config (毛麾, etc. )

Coding Giga !¶

- How to update help message DOD叩叩更D 庄叩D ver. 叩 DODO叩OD叩叩叩叩D_Dr_Zhuang_Ver.pptx

Dr. Zhuang's Comment:

□□叩option或叩function叩叩对叩 23-25 页叩内叩

22页伲man库叩叩叩。叩们叩前叩操叩是叩叩叩本叩后叩更□叩叩push叩GerritD review

- How to update man page : man_page_guide_20240108.pdf

- Check overall code structure with slides Code_overview.pptx

- Check the general command interface (C, Tcl, Python) with slides add_new_commands.pptxadd_python_command.pdf

- Check the command interface (C implementation) with slides VP_cmd_interface.pptx

- Check how to read and debug and profile GIGA code (basic version) Read_debug_giga_code_1.pptx

More details in http://10.30.200.21:8088/projects/hongtu-emir/wiki/Coding

More debug details in http://10.30.200.21:8088/projects/hongtu-emir/wiki/Debugging_and_profiling_tech

Timing Analysis New Hire Training¶

- Check timing background and materials in http://10.30.200.21:8088/projects/hongtu-sta/wiki

- The timing analysis basic introduction I VLSI_ta_p376_386.pptx

- The timing analysis basic introduction II VLSI_ta_practical.pptx

500 - STA 0经叩D (by Daisy Li)

Power Analysis¶

- Check power background slides I and II EDA_PA_basic_I.pptx

- Power analysis training lab guidance (TBD.)

- Advanced power analysis background: http://10.30.200.21:8088/projects/hongtu-emir/wiki/Power_analysis

- Low power design flow: http://10.30.200.21:8088/projects/hongtu-emir/wiki/Low_power_design_flow_and_training

GUI and UI¶

- All about TCL, UI, GUI: http://10.30.200.21:8088/projects/understand-aguda/wiki/Aguda_GUI

- TCL new-hire training: http://10.30.200.21:8088/projects/understand-aguda/wiki/New_hire_checklist

RC Extraction New Hire Training:¶

PR Related New Hire Training:¶

- Check New-hire page: http://10.30.200.21:8088/projects/understand-detailed-placement/wiki/New_hier_related

Logic Synthesis New Hire Training:¶

- Check Main Page: http://10.30.200.21:8088/projects/hongtu-logicsynth/wiki

- New training page: http://10.30.200.21:8088/projects/hongtu-logicsynth/wiki/Wiki

Level-3 Core engine and math¶

Please check Advanced_EM-IR_Center , these are core math ideas behind Giga core engine!□

Updated by jun chen 5 months ago · 10 revisions