RC parasitic extraction and LPE¶

ESD¶

□5田0片0叩D叩陈叩□ 博叩~0

ESD background introduction: Giga_DA_ESD_Models_Devices_and_Analysis.pptx

ESD reference paper: ming-douker1999.pdf (From Dr. Shi)

ESD reference paper: 02_Simulating_Electrostatic_Discharge.pdf (From Jeff)

ESD online training: https://www.bilibili.com/video/BV1C34y1p7Jk?share_source=copy_web&vd_source=d04eb1abca6ba586bf0375f4ee96ad31 (From Dr. Chen)

LVS¶

LVS introduction: http://10.30.200.21:8088/projects/hongtu-emir/wiki/LVS_introduction

Resistance and capacitance¶

Professional link (By Xu): http://10.30.200.21:8088/projects/understand-aguda/wiki/Understand_LPE

Professional introduction (By Xu): http://10.30.200.21:8088/projects/understand-aguda/wiki/LPE_Basic

Cap and resistance introduction¶

Background knowledge (where cap comes from): ECE4121Lec08Wire.pdf , CapacitanceDrivingaLoadannotated.pdf

IR analysis cap contributor: about_cap_clean.pptx

Resistance usage model and background: Resistance_analysis_and_report.pptx

Chip_RC_Correlation¶

Regression and QA method¶

Regression location: ut/tests/ut/vp/ir/resistance

Regression command 1: qa_report_pg_resistance

Regression command 2: qa_report_detail_regression

Regression command 3(obsolete): qa_analyze_power_network res golden_res_file test_res_file

Effective resistance¶

New usage

analyze—pg—resistance -net VDD -effective [-generate—supply—location (hidden option)]

髻 by default, 10 worst instance will be reported. if -number—of—worst set to 0 or negative, report

all

report—pg—resistance -net VDD -effective [-number—of—worst 10] report—pg—resistance -net VDD cell—name -effective

髻 will dump all the result to file

report—pg—resistance -net VDD -effective -number—of—worst 0 -output—file xxx.rpt

髻 will show heat map in G·r without re-build graph show—effective—resistance—map

髻 below error out since -detail only support in min-path mode report—pg—resistance -net VDD cell—name -detail

Old usage:

set—app—var ir calc—resist—mode Fl.AT

analy江e—power—network -net VDD -res—only [-generate—supply—location]

report—power—network -net VDD -type res

Min-path resistance¶

New usage

analy江e—pg—resistance -net VDD [-generate—supply—location (hidden option)]

髻 by default, 10 worst instance will be reported. if -number—of—worst set to 0 or negative, report all

report—pg—resistance -net VDD [-number—of—worst 10] report—pg—resistance someCell -high—light -detail -net VDD

髻 will dump all the result to file

report—pg—resistance -net VDD -number—of—worst 0 -output—file xxx.rpt

髻 will show up heat map in G·r, power min-path, ground min-path, total min-path will display

髻 if a cell is not connected to power/ground, the color annotation will be skiped. rn the total re sistance calculation, the un-connected net res is regarded as 江ero.

show—min—path—resistance—map

Old usage:

set—app—var ir calc—resist—mode S:ORTPAT:

analy江e—power—network -net VDD -res—only [-generate—supply—location] report—power—network -net VDD -type res -inst xxx -high—light report—power—network -net VDD -type res -path—number 4

Debug pg resistance¶

See Generic testing SoP:

http://10.30.200.21:8088/projects/hongtu-emir/wiki/Generic_Testing_SoP#section-10

Open-short and missing via check¶

verify—power—network

check—pg—vias

- :VP O 叩 check—pg—vias D叩D叩D叩D叩D叩D叩missing viaD

get—ob“—attr [get—violations -checker pgroute] bbox - :VP O 叩 verify—power—network D叩D叩D叩D叩D叩D 叩 open/short/floating (open D叩D )D

get—ob“—attr [get—violations -checker layout—verifier -filter—by {rule == open}] bbox

Regression location¶

ut/tests/ut/vp/ut_run/ir/resistance/xxx

VIA resistance (TBD.)¶

analy江e—via—resistance

compare resistance by layer¶

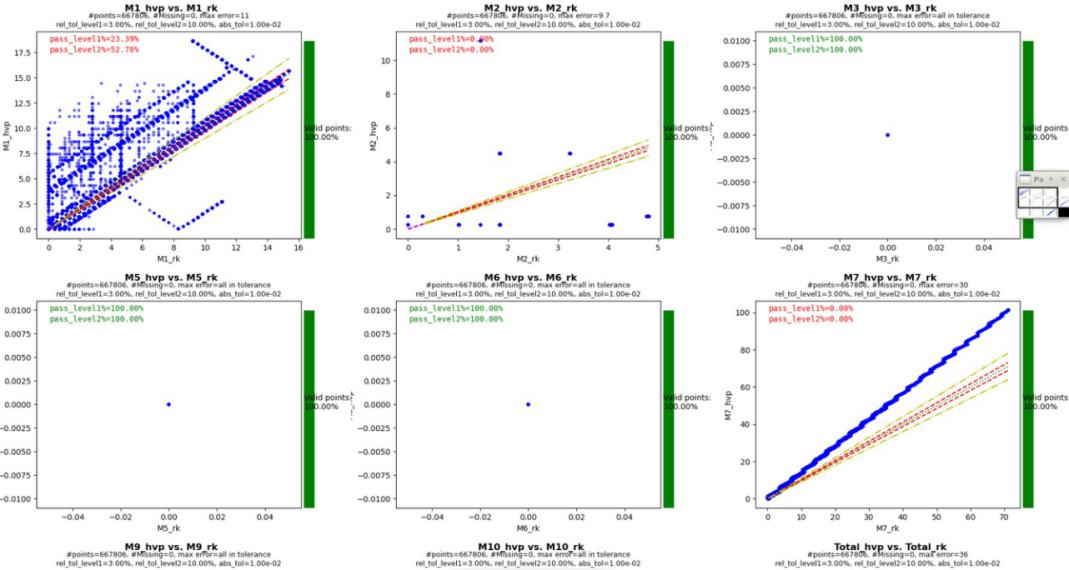

DDDDD D min-path D叩D叩D叩D叩叩叩D叩度叩0叩D叩D叩D叩D叩D叩叩叩总叩叩叩叩叩映叩D叩导叩ir叩叩叩em叩叩叩

D 叩D叩D叩DD叩D叩叩叩叩res改叩就叩须叩D static irDDDDDD叩DDDDDD叩DD希叩□ :VP D Ref tool D detail res 门叩叩叩叩叩D叩D叩

DDD□ :VP D Ref tool D min res detail path门叩叩叩叩叩D叩叩并叩D叩叩叩叩叩

D叩D

compare—detail—path—resistance -input—file minPath.rk [-output—file compare.result] [-plot—scatter

]

□叩flowD

...

set—app—var ir save—graph true analy江e—pg—resistance

compare—detail—path—resistance -input—file minPath.rk -output—file compare.result

DDDinput_fileDredhawkOmin resistance detail path report, D叩DD叩

output_fileDDDDDDODDDDDD叩DD叩

DDDD-plot_scatterDDDDDDDDD田叩

RC extraction¶

About rlc model¶

RCGEN_USAGE.pdf (from XuLuo 20230905)

Base method (Obsolete)¶

DDDD layer D DD叩叩DDDDDDD叩叩叩DD 叩 (DD D rlc DODD )

1.D叩 1叩set—linear—unit—rlc (DD叩叩叩叩叩叩D导叩叩叩DD候 叩 unitR / width * length

D DDDDD叩DDDDDDDDD叩D叩叩叩叩DDD叩DDDDDDDDDDD

2.D叩 2叩 set—resistance—table (DODDD伲插叩叩 叩 叩D导叩叩叩DD候 叩 lpm->CalcMetalR叩叩DD导叩叩叩

D DD叩DD叩叩DD叩D叩D叩DDD

D叩 1DDD叩D叩DD signoff emirDD叩DDD叩D叩 2DD叩

Advanced method: (New engine from Xu, after 20220310)¶

See: http://10.30.200.21:8088/issues/7418

first phase changes:

1.ir rc_multi_threads 1: valid in "ir rc_mode 2", changed to on by default

2.ir rc_keep_pg_only 0: valid in "ir rc_mode 2", new, off (high accuracy) by default, will be on (medium accuracy, aligned with RH, equivalent to internal param "ir rc_ignore_mode 0x248") controled by other new coming ir params (like "ir accuracy_level high", will be followed up by Jun)

3.ir rc_mode 0/1/2: 0 existing auto-mode, will be retired, 1 forcedly unitR/C, 2 exact RC extraction like signal (will be on by default for signoff VP, followed up by Jun), no further change for now.

todo list:

1.px dont_extract_cap 1: on by default for static IR-drop analysis if "ir rc_mode 2" is set

2.new ir param (e.g., accuracy_level medium [ I low I high]), to be discussed with Jun to turn on below params:

low:

ir rc_mode 1

medium:

ir rc_mode 2

ir rc_keep_pg_only 1

high:

ir rc_mode 2

ir rc_keep_pg_only 0

3.change default value for below two params:

3.1param "ir rc_keep_pg_only_tv 1" : change default from 0 to 1 for thickness variation.

3.2param "ir rc_keep_pg_only_cap 1": change default from 0 to 1 for cap weighting factor.

Advanced method: (Default method in EMIR Obsoleted after 20220310)¶

D叩 signal RC 引叩D叩PG RC:

set—app—var ir rc—mode 2

to enable MT run (temp param, default off for now, could be on by default if stable): set—app—var ir rc—multi—thread 1

D叩rlcDDD叩PG RC:

调叩resistance D capacitance ODD叩列DD叩 D田RC□DDDD

-

DDDDDDDDDDDDDDDDDOresDcapDO叩

set—app—var ir rc—mode 1

髻 for debug for debug purpose set—app—var ir debug—rc 1 -

DDDDDDDDD DDODDDDDDDODDDDDDDDDDDDDDDDDDDDDDDDDrlcDDDOetchingDD

髻 default minimal spacing 3.5 set—app—var ir r—spacing—factor 1.5 set—app—var ir c—spacing—factor 1.5 -

DD02DDworkD叩叩DDparamD

50micron X 50micron DDDtableDDDDDDwindowDODDDDDDDDD

set—app—var ir r—density 1.5 set—app—var ir c—density 1.5 -

DDD叩甩叩 R C spacing factor: ooD加O app_var 有叩高叩先叩

set—pg—rc—config -

verify resistance value by

report—pg—rc -layer M1 -area {llx lly urx ury}

report pg rc for "ir mode 2" using sigal like RC extraction model report—pg—rc -bbox {llx lly urx ury} -net VDD -layer M1

Example: if a wire start from 2327.765 to 2330.39, width is 0.15 micron. Run below command to check rc engine

set—app—var rc—mode 2

report—pg—rc -bbox {232l.l65 3354.l8-0.0l5 2330.39 3354.l8+0.0l5 } -net DVDD

- test case and data

about spef¶

判叩 spef DDDD叩 lpe::HasFileRC

- import rlc model by (From Xu Luo):

after source .rlc file, you shall set the command "set—parasitic—condition cmax" for l.PF module to use this cmax model.

besides, you may report pg rc by setting -length/-width,

e.g., "report—pg—rc -layer M1 -length 10 -width 1" instead of "report—pg—rc -layer M1",

as empty -length/-width is equivalent as 江ero length/width for the command.

RC for DMP¶

DDDD田DDDDDcacheDDDDDDDD

"analy江e—pg—resistance -net VDD"

"cache—pg—resistance db -net VDD -graph—name "vdd.pgraph1" " //当DD叩□ cache叩二叩制DO叩

masterD叩DD田DDDDDload DDDOpgraph DDDDDDDDDpgraphDD行DDDOD

"restore—pg—graph db -net VDD -graph—name "vdd.pgraph1 vdd.pgraph2 .... " " //当DD叩□ cache叩二叩制DO叩

sanity resistance check¶

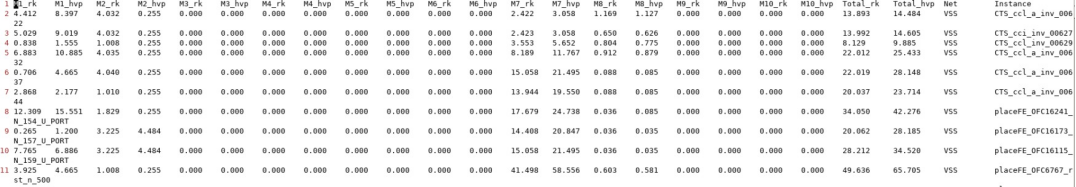

D田田D轻叩DrlcDD叩测Dhvp compose_top_design DDsource D rlcDDD就田田D始D行叩测DD叩根叩叩Dref toolOmin pathDD成叩样D叩叩工叩叩

"sanity—check—resistance -detail—path—file reftool—min—path.rpt -path—limit 10 -layer—sample—limi t 10 -error—tolerance—threshold 0.2 -output—report out.rpt"

-detail—path—file

:DD ref tool □□D min path report叩DDD叩DDD O D叩旧伲D layer 叩 叩 space 叩width 叩 density叩 golden res叩DD hvpDD叩h vp叩D引伲叩DDD hvpD res叩 DD D golden res D diff叩

-path—limit: D ref toolDD旧伲D少叩min path叩default D 10

-layer—sample—limit : D ref toolDD layerD旧伲DDDD叩default D 10

-error—tolerance—threshould : D D hvp res D golden resD diff tolerance叩叩叩范叩

-output—report: DD输叩DO

DB00DD经叩□叩

DD叩DDDDBODDDDDODD□叩叩

ref tool run RC check

DDDrun ref toolOresistance analysis□□D田田田D□D田DinstanceOeff/min resistanceD叩田田田D得DDDinstanceOeff/minODDD

"perform res—calc -thread 8 -loopmode -instFile fileName -o ./adsRpt/effective—res.rpt"

// DDD fileNameDDD叩DDDD instance name(DD叩DD instance name)

叩D叩DD□DD instD eff resDDDDDDO叩effective—res.rpt叩

"perform min—res—path -instFile instFileName -simplified—report -o ./adsRpt/min—path—res.rpt "

//DDD instFileNameDDD叩DDDD instance name(DD叩DD instance name)

叩D叩DD□DD instD min path DDDDDDO叩min—path—res.rpt叩叩

Dwukong runDDDcase

DD designDDD

/reg/wukong/wukong u七 -b {binary} -d {case pa七h} -q {queue} -k DODD

1.DDinpu七DDDDDDgoldenDDD

2.DDDDDD七es七.七cl

切□designODD

partition—top—design -colu 3 -row 3 -verbose

//DDD叩D□ top designOO 3x3DD叩00D□叩叩DD 叩 .hvp—partition—data DO0叩D partition—top—design -region {left—bottom—x left—bottom—y right—top—x right—top—y}

partition—top—design -region {0 20.0 100.0 200.0}

叩叩叩叩DDDDDDD Probe NodeDD叩叩叩叩

-

DDDD probe node

add—pg—probe—node -net VDD -layer "metal1" -name test—node -location {100 200}

analy江e—pg—resistance -net VDD -virtual—mode -

叩DOD叩DDDD probe nodes

add—pg—probe—node -probe—file probe—file.csv

analy江e—pg—resistance -net VDD -virtual—mode DODDD叩D

髻net—name metal—name x y current

| VDD | metal1 | 100 | 200 |

| VDD | metal1 | 300 | 400 |

叩static ir叩DDDDDDD Probe NodeDD叩叩叩叩

-

DDDD probe node

add—pg—probe—node -net VDD -layer "metal1" -name test—node -location {100 200}

analy江e—static—ir—drop -virtual—mode -

叩DOD叩DDDD probe nodes

add—pg—probe—node -probe—file probe—file.csv analy江e—static—ir—drop -virtual—mode

DODDD叩D

髻net—name metal—name x y current VDD metal1 100 200 0.1

VDD metal1 300 400 0.01

...

Debug resistance SOP:¶

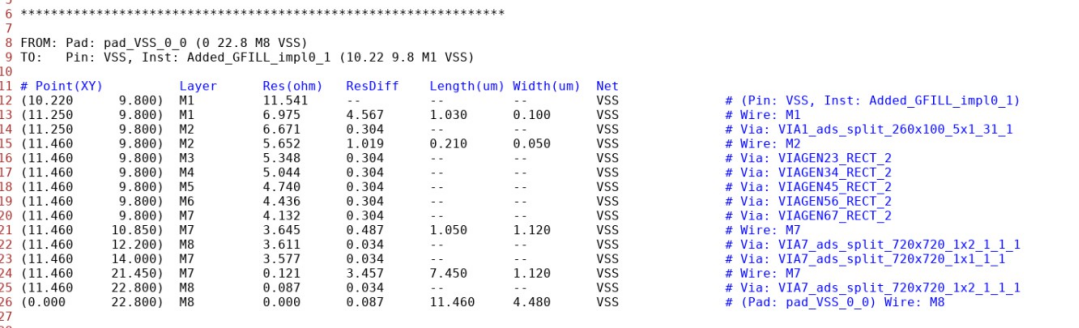

debug min path resistance:¶

debug eff resistance:¶

eff叩叩叩0DD SOP叩叩版叩

1.□叩by-layer res scatter DD叩D叩叩DD叩D叩DDDDDDDDD叩D metalD叩

compare—detail—path—resistance -input—file rh—golden—detail—paht.rpt

2.D叩D叩DD metal DDD伲metalD diffDDD instance叩

3.叩hvpD rh叩别门叩伲instanceDDD伲叩叩叩D path叩(rhD叩直伲grep report file)

□DD golden rhD伲叩D0叩hvpDDDD叩D叩debug—pg—resistance

4.2 D0D叩0叩叩00

□DDD叩metalD叩叩DD叩叩邻DDDD叩叩0叩D0D叩叩0叩D叩report—pg—rc 门D叩rh伲叩DD叩叩叩hvpDD叩DDD叩

debug resistance report:¶

- set—app—var node—reduction—effort -1 //D叩node reduction防叩干叩叩叩

DBDDDD :¶

-

set_site:

叩tech fileD叩DD叩set—siteDDDD MACRO,叩O D heightDDDDD default cell height -

DDDOregression:

vp—regression -d -r {ut—run/}case伲 叩 //唯D叩 叩 ut—run伲叩D需叩

叩wukongDDO case

/reg/wukong/wukong ut -b {binary} -d {case path} -q {queue} -k

3.ODprofile0叩:

vi Makefile.hvp FXPORTFD—DFFrNFS:=-D—B·rl.D—VP=1 -D—FMrR—PROFrl.F=1 叩叩DO叩ODODD PROFrl.FR()

- compose_top_designDD

D D叩D emirTcl·tilityFlow.tcl

assemble—physical—top—design

- 产加rlcDDDD

!58F3D26l-84F2-4l40-ABlF-A8F2F8B3FB49!

本叩□□明D rlcDO

RCGFN -no—auto—enc□叩明D rlc DDDD叩D叩D叩D叩□□ viaD rlc

lp—test dump—rlc—via -rlc—model <model—name> -layer <vial.ayerName>

list—rlc—model 显伲hvp rlc信叩

6. 产加OT techDDDD

D itf□□ techDO

rhtech -i itf.name D ircx□□ techDO

ircx2tech -i ircx.name

- OTAKU local run DD□D

叩田地叩: /home/ljxie/emir_tools/check_sum.csh

1.且DD己Orun dataDD(

)

2.0 行叩田

- 叩Dhtml main branchDDD localODDD叩叩田叩叩加DDDDD叩加DD再叩DDD田

出叩graph edgeDDDDD SOP:

1.check input D入D田叩DDDD

2.田D版田田叩DDDD

3.node reduction -1;

4.debug_pg_resistance -location {x1 y1}; // report 田Dnode DDOpgraphD田0叩D 5.set_power_network_mode -area {x1 y1 x2 y2} //甩叩田D叩D□D区叩

Updated by jun chen 4 months ago · 6 revisions